ARAB ACADEMY FOR SCIENCE, TECHNOLOGY AND MARITIME TRANSPORT

**College of Engineering and Technology**

**Electronics & Communications Engineering Department**

# EFFICIENT DESIGN AND IMPLEMENTATION OF DVB-T2 MODULES ON FPGA

By

Eng. Hesham Ahmed Fahmy Amin

A dissertation submitted to AASTMT in partial fulfillment of the requirements for the award of the degree of

# **MASTER of SCIENCE**

In Electronics and Communications Engineering

# Supervisors

### Prof. Khaled Ali Shehata

Electronics & Communications Engineering Department Arab Academy for Science, Technology and Maritime Transport, Alexandria, Egypt.

## Dr. Safa Mohamed Gasser

Electronics & Communications Engineering Department Arab Academy for Science, Technology and Maritime Transport, Cairo, Egypt.

### ACKNOWLEDGEMENTS

I am very grateful to **ALLAH** Subhanahu Wa Ta'ala who gave me an excellent family to live with and provided me the environment where I could finish my M.Sc. and without whose will it would have been impossible to complete my degree.

Second only to **ALLAH**, thanks to my parents Prof. Dr. Ahmed Fahmy and Donia Mohamed Kamel for what they have contributed towards my education and my whole life. Their unconditional love, constant support, great advice and prayers over the years are something that I cannot thank them for enough. Additionally, knowing that my success in completing my M.Sc. would be a source of happiness for them, I was further motivated to work hard.

I would like to express my heartily thanks to my wife Eng. Dina Tarek who always encouraged me in this challenge and in filling the gaps. At times, when things looked difficult, she was the one who gave me hope.

My deepest appreciation goes to my advisor **Prof. Dr. Khaled** for his active contribution to refining my research work. He was there to listen to my concerns, review the material, provide feedback and show direction.

Similarly, I thank **Dr. Safa** for her support in improving my understanding of the DVB-T2 system background and her suggestions during the research.

ii

Special thanks to my friends. They always encouraged me in this challenge. This goes especially for **Eng. Fadi Ayad** and **Eng. Khaled Salem** for their support.

I gratefully acknowledge the staff of the Electronics and Communications Engineering Department for providing me with support and convenience during my studies at the Arab Academy for Science, Technology and Maritime Transport.

### ABSTRACT

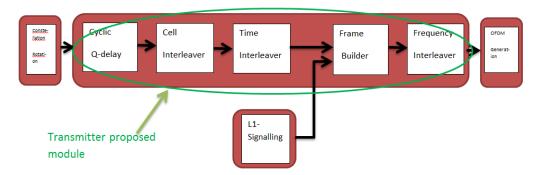

DVB-T2 (The second generation Digital Video Broadcasting) is a system enhancement compared to the DVB-T system. The main motivation of DVB-T2 is to provide broadcasters with more reliable, advanced and efficient alternative to DVB-T standard. The cyclic Q delay, cell interleaver and time interleaver are optional modules employed in the DVB-T2 system. The main purpose of these modules is to increase the overall performance of the DVB-T2 system. The cell mapper module is used to build the T2 frames and hence the T2 super frames. The frequency interleaver module which applies a permutation to the T2 frames is employed in the system to increase the ability of data recovery when faces the channel noise.

Combining Cyclic Q delay, cell interleaver, time interleaver, cell mapper and frequency interleaver modules into one single module is the thesis goal. The combination is to decrease the system complexity, hardware usage and the overall system delay and hence increase the overall DVB-T2 system performance. In this thesis we propose a new module to combine these modules. The new module is simulated and hardware implemented.

| TABL | E OF | CONT | TENTS |

|------|------|------|-------|

|------|------|------|-------|

| CHAI | PTER 1    | INTRODUCTION                                               | 1        |

|------|-----------|------------------------------------------------------------|----------|

| 1.1  | Introduct | ion                                                        | 1        |

| 1.2  | General b | background                                                 | 1        |

| 1.3  | Research  | Objective and Thesis Outline                               | 2        |

| CHAI | PTER 2    | DIGITAL VIDEO BROADCASTING (DVB)                           | 3        |

| 2.1  | Introduc  | tion                                                       | 4        |

| 2.2  | Digital T | Felevision Standards                                       | 4        |

|      | 2.2.1     | Advanced Television System Committee                       | 4        |

|      | 2.2.2     | Integrated Services Digital Broadcasting                   | 6        |

|      | 2.2.3     | Digital Video Broadcasting                                 | 7        |

| 2.3  | Differen  | t DVB Standards                                            | 8        |

|      | 2.3.1     | Digital Video Broadcasting- Satellite                      | 8        |

|      | 2.3.2     | Digital Video Broadcasting- Satellite Second Generation    | 10       |

|      | 2.3.3     | Digital Video Broadcasting-Cable                           | 12       |

|      | 2.3.4     | Digital Video Broadcasting-Cable Second Generation         | 13       |

|      | 2.3.5     | Digital Video Broadcasting-Handheld                        | 15       |

|      | 2.3.6     | Digital Video Broadcasting – Terrestrial                   | 16       |

|      | 2.3.7     | Digital Video Broadcasting – Terrestrial Second Generation | 18       |

| 2.4  | Conclusi  | ion                                                        | 19       |

| CHAI | PTER 3    | DIGITAL VIDEO BROADCASTING – SECOND<br>GENERATION (DVB-T2) | 19       |

| 3.1  | Introduct | ion                                                        | 20       |

| 3.2  | DVB-T2    | transmitter                                                | 20       |

|      | 3.2.1     | Input processor                                            | 21       |

|      |           | 3.2.1.1 Mode Adaptation                                    | 21       |

|      |           | 3.2.1.2 Stream Adaptation                                  | 24       |

|      | 3.2.2     | Bit Interleaved Coding and Modulation (BICM)               | 25       |

|      |           | 3.2.2.1 FEC encoding                                       | 22       |

|      |           | 3.2.2.2 Bit interleaver                                    | 22<br>26 |

|      |           | 3.2.2.3 Bit to cell word de-multiplexer                    | 28       |

|               | 3.2.2.4    | Mapping and Constellation Rotation      | 28       |

|---------------|------------|-----------------------------------------|----------|

|               | 3.2.2.5    | Cyclic Q-Delay                          | 31       |

|               | 3.2.2.6    | Cell Interleaver                        | 21       |

|               | 3.2.2.7    | Time Interleaver                        | 31<br>32 |

| 3.2.3         | Frame Bu   | uilder                                  | 32<br>34 |

|               | 3.2.3.1    | Cell Mapper                             | 34       |

|               | 3.2.3.2    | Frequency interleaver                   | 36       |

| 3.2.4         | OFDM ge    | eneration                               | 37       |

|               | 3.2.4.1    | Pilot Insertion                         | 37       |

|               | 3.2.4.2    | IFFT–OFDM Modulation and Guard Interval | 38       |

| 3.3 DVB-T2    | Receiver   |                                         | 39       |

| 3.3.1         |            | eceiver Block                           | 39       |

| 3.3.2         | Frame Bui  | ilder Block                             | 39       |

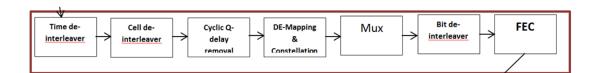

| 3.3.3         | Bit Deinte | rleaved and Coded Demodulation Block    | 41       |

| 3.4 Conclusio | on         |                                         | 42       |

# CHAPTER 4 MATLAB SIMULATION OF THE DVB-T2 43 SYSTEM MODULES 43

| 4.1 | Introduc | ction                    | 43 |

|-----|----------|--------------------------|----|

| 4.2 | Transmi  | itter Simulation         | 43 |

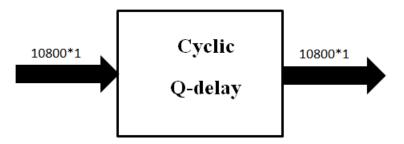

|     | 4.2.1    | Cyclic Q-delay           | 44 |

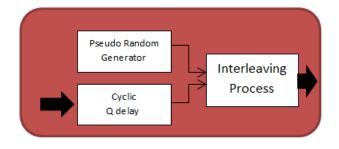

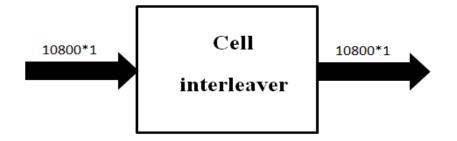

|     | 4.2.2    | Cell interleaver         | 46 |

|     | 4.2.3    | Time interleaver         | 49 |

|     | 4.2.4    | Cell Mapper              | 51 |

|     | 4.2.5    | Frequency Interleaver    | 52 |

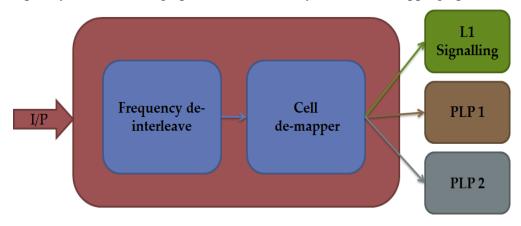

| 4.3 | Receive  | er Simulation            | 54 |

|     | 4.3.1    | Frequency De-interleaver | 55 |

|     | 4.3.2    | Inverse frame builder    | 55 |

|     | 4.3.3    | Time de-interleaver      | 56 |

|     | 4.3.4    | Cell de-interleaver      | 57 |

|     | 4.3.5    | Cyclic Q-delay removal   | 58 |

| 4.4 | Conclus  | sion                     | 59 |

# CHAPTER 5 HARDWARE IMPLEMENTATION

| 5.1 | Introduction |                    |                                                                 | 60 |

|-----|--------------|--------------------|-----------------------------------------------------------------|----|

| 5.2 | DESIGN AN    | D IMPLEMENTA       | TION STEPS                                                      | 61 |

| 5.3 | Implementat  | ion of the QCTCF N | Module                                                          | 63 |

|     | 5.3.1        | The QCT Module     |                                                                 | 64 |

|     |              | 5.3.1.1            | Cyclic Q Delay                                                  | 65 |

|     |              | 5.3.1.2            | Cell Interleaver                                                | 67 |

|     |              | 5.3.1.3            | Combining cyclic Q delay with cell interleaver operations       | 69 |

|     |              | 5.3.1.4            | Time Interleaver                                                | 71 |

|     |              | 5.3.1.5            | Combining cyclic Q-Delay, cell Interleaver and time Interleaver | 72 |

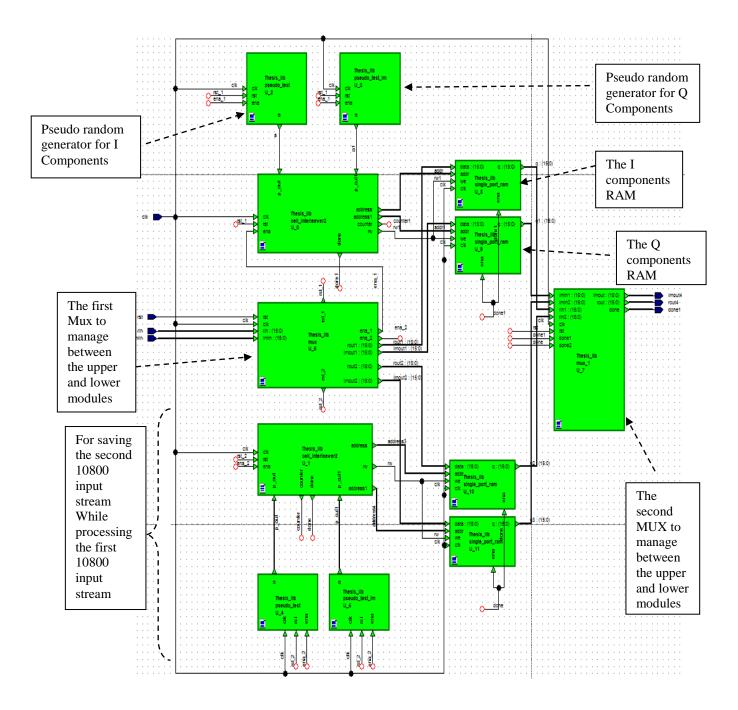

|     |              | 5.3.1.6            | Implementation of the QCT module                                | 74 |

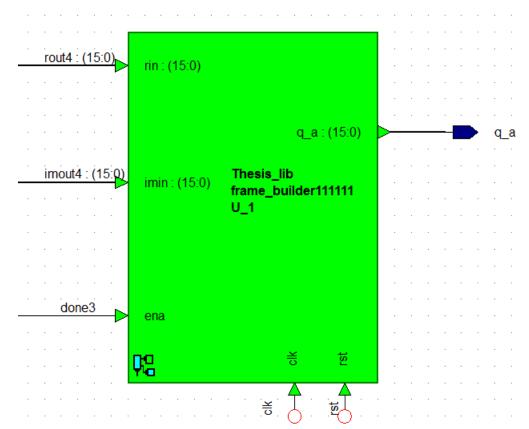

|     | 5.3.2        | The CF Module      |                                                                 | 79 |

|     |              | 5.3.2.1            | The Cell Mapper                                                 | 80 |

|     |              | 5.3.2.2            | The Frequency Interleaver                                       | 81 |

|     |              | 5.3.2.3            | Combining the Cell Mapper with the<br>Frequency Interleaver     | 82 |

|     |              | 5.3.2.4            | Implementation of the CF Module                                 | 83 |

| 5.4 | Synthesis    |                    |                                                                 | 88 |

| 5.5 | Conclusion   |                    |                                                                 | 89 |

60

| CHAPTER 6 | CONCLUSION AND FUTURE | 90 |

|-----------|-----------------------|----|

|           |                       |    |

| 6.1 | Conclusion   | 90 |

|-----|--------------|----|

| 6.2 | Future Work  | 91 |

|     |              |    |

| DET |              | 02 |

| REF | FERENCES     | 92 |

| ARA | ABIC SUMMARY | 96 |

# LIST OF ABBREVIATIONS

64-QAM 64-ary Quadrature Amplitude Modulation ATSC Advanced Television Systems Committee ACM Adaptive Coding and Modulation **Base Band** BB BCH Bose-Chaudhuri-Hocquenghem error correcting code Bit De-interleaved and Coded Demodulation **BDCD** BICM Bit Interleaved Coding and Modulation CI Cell Interleaver CRC Cyclic Redundancy Check Data Field Length DFL DTV **Digital Television** DVB **Digital Video Broadcasting** DVB-T DVB for terrestrial broadcasting DVB-T2 DVB-T second generation as specified in the present document FEC Forward Error Correction FEF **Future Extension Frame** FFT Fast Fourier Transform GCS Generic Continuous Stream GS Generic Stream HDTV High Definition Television IFFT Inverse Fast Fourier Transform ISDB Integrated Services Digital Broadcasting LDPC Low Density Parity Check LSB Least Significant Bit Moving Pictures Experts Group MPEG Most Significant Bit MSB Normal Mode NM OFDM **Orthogonal Frequency Division Multiplexing** Peak to Average Power Ratio PAPR Physical Layer Pipe PLP PRBS Pseudo Random Binary Sequence **OPSK** Quaternary Phase Shift Keying RF **Radio Frequency** RS Reed-Solomon TFS Time Frequency Slicing TS **Transport Stream** UP User Packet User Packet Length UPL Very High Speed Integrated Circuits VHDL

# LIST OF FIGURES

| Figure  | Caption                                                           | Page |

|---------|-------------------------------------------------------------------|------|

| 2.1     | ATSC Block Diagram                                                | 5    |

| 2.2     | ISDB Block Diagram                                                | 6    |

| 2.3     | DVB Block Diagram                                                 | 7    |

| 2.4     | DVB-S Block Diagram                                               | 8    |

| 2.5(a)  | MPEG-2 Transport Mux Packet                                       | 9    |

| 2.5(b)  | Randomized Transport Packets                                      | 9    |

| 2.5(c)  | (204,188,8) Reed Solomon error protected packets                  | 9    |

| 2.6     | DVB-S2 Block Diagram                                              | 11   |

| 2.7     | DVB-C Block Diagram                                               | 12   |

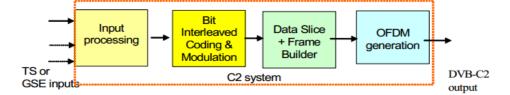

| 2.8     | High level C2 Block Diagram                                       | 13   |

| 2.9(a)  | Mode adaptation for single input stream (PLP)                     | 13   |

| 2.9(b)  | Bit Interleaved Coding and Modulation (BICM)                      | 13   |

| 2.9(c)  | Data Slice + Frame builder                                        | 14   |

| 2.9(d)  | OFDM Generation                                                   | 14   |

| 2.10    | Additions brought to the DVB-T system by DVB-H                    | 15   |

| 2.11    | DVB-T Block Diagram                                               | 16   |

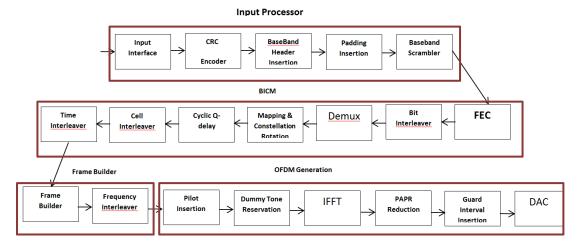

| 3.1     | High level T2 block diagram                                       | 20   |

| 3.2     | DVB-T2 block diagram                                              | 21   |

| 3.3     | DVB-T2 Input Processor                                            | 21   |

| 3.4     | CRC Algorithm                                                     | 22   |

| 3.5(a)  | NM header format                                                  | 23   |

| 3.5(b)  | HEM header format                                                 | 23   |

| 3.6     | PRBS Implementation                                               | 24   |

| 3.7     | BICM Block Diagram in DVB-T2 system                               | 25   |

| 3.8     | Format of data before bit interleaving                            | 25   |

| 3.9     | Bit Interleaving scheme                                           | 27   |

| 3.10    | De-multiplexing of bits into sub-streams                          | 28   |

| 3.11    | 16- QAM constellations                                            | 29   |

| 3.12(a) | Classic 16-QAM constellations with projections in axis (2x 4-PAM) | 30   |

| 3.12(b) | Rotated 16-QAM constellations with projections in axis (2x16-PAM) | 30   |

| 3.13    | Cyclic Q-delay process                                            | 31   |

| 3.14    | Cell Interleaver process                                          | 32   |

| 3.15    | Time Interleaving Implemented in DVB-T2                           | 33   |

| 3.16    | Frame Builder                                                     | 34   |

| 3.17    | Cell Mapper Frame Structure                                       | 34   |

| 3.18   | Frequency interleaver algorithm for the 16k mode              | 36 |

|--------|---------------------------------------------------------------|----|

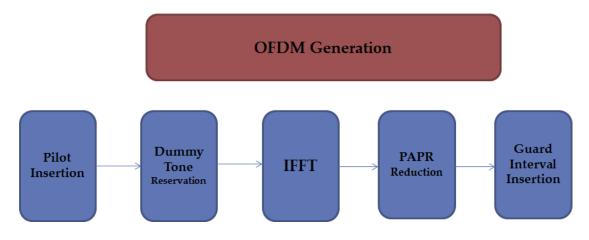

| 3.19   | OFDM generation Block                                         | 37 |

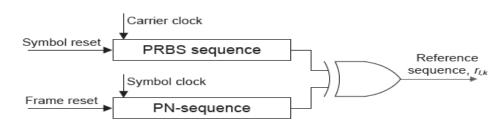

| 3.20   | Formation of the reference sequence                           | 38 |

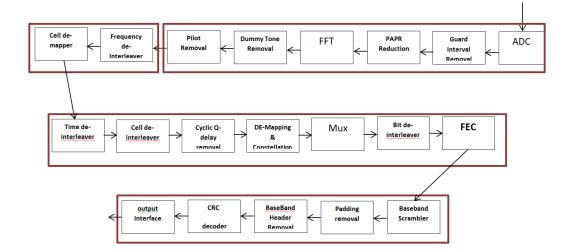

| 3.21   | DVB-T2 system Receiver                                        | 39 |

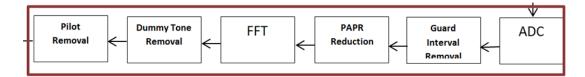

| 3.22   | OFDM receiver block diagram                                   | 40 |

| 3.23   | Frame builder at the receiver                                 | 40 |

| 3.24   | Bit De-interleaved and Coded Demodulation Block Diagram       | 41 |

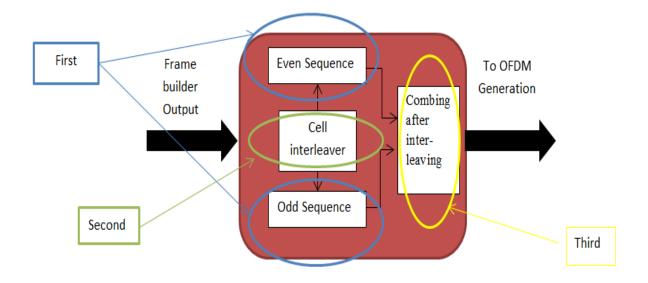

| 4.1    | Transmitter proposed module                                   | 43 |

| 4.2    | Cyclic Q-delay operation                                      | 44 |

| 4.3    | Cyclic Q-delay module input output dimensions                 | 45 |

| 4.4(a) | Cell interleaving process                                     | 47 |

| 4.4(b) | Input to the cell interleaver (example)                       | 48 |

| 4.4(c) | Pseudo random generator output (example)                      | 48 |

| 4.4(d) | The cell interleaving output (example)                        | 48 |

| 4.5    | Cell interleaver input output dimensions                      | 48 |

| 4.5    | Bit Interleaving scheme for normal FECFRAME length and 16-QAM | 47 |

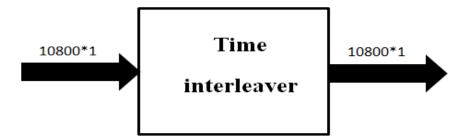

| 4.6    | Time interleaver input output dimensions                      | 48 |

| 4.7    | Time interleaver operation for 64 QAM                         | 50 |

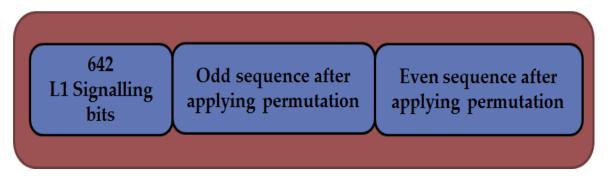

| 4.8    | Frame builder                                                 | 51 |

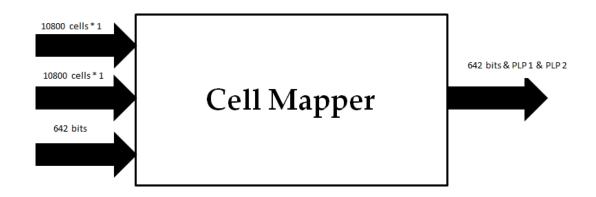

| 4.9    | The cell mapper input output dimensions                       | 52 |

| 4.10   | Frequency interleaver operation                               | 53 |

| 4.11   | The frame builder output                                      | 53 |

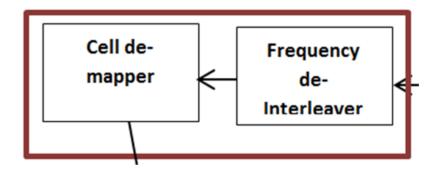

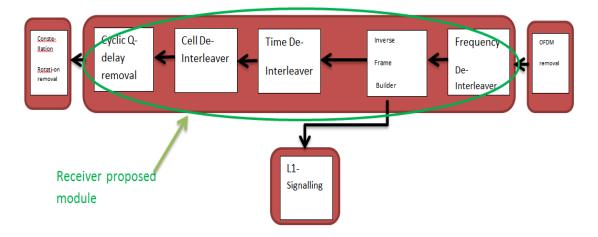

| 4.12   | Receiver Proposed Module                                      | 54 |

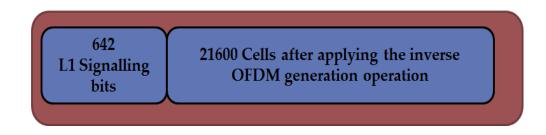

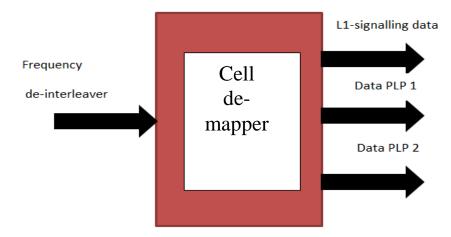

| 4.13   | The inverse frame builder                                     | 54 |

| 4.14   | The frequency de-interleaver input data stream                | 55 |

| 4.15   | Inverse cell mapper module                                    | 55 |

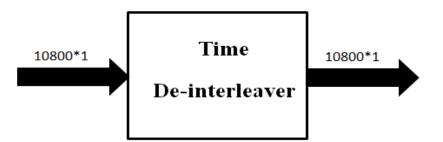

| 4.16   | Time de-interleaver input output dimensions                   | 56 |

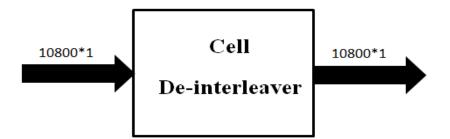

| 4.17   | Cell de-interleaver input output dimensions                   | 57 |

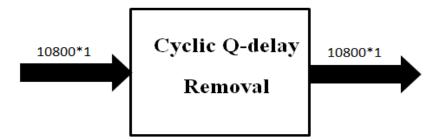

| 4.18   | Cyclic Q-delay Removal input output dimensions                | 58 |

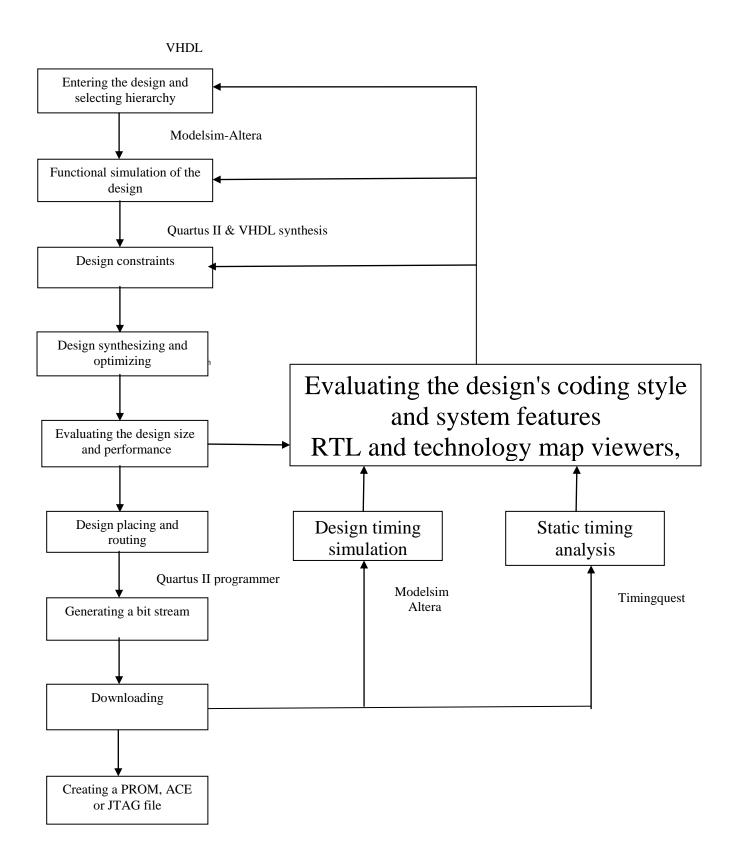

| 5.1    | Design and implementation steps                               | 62 |

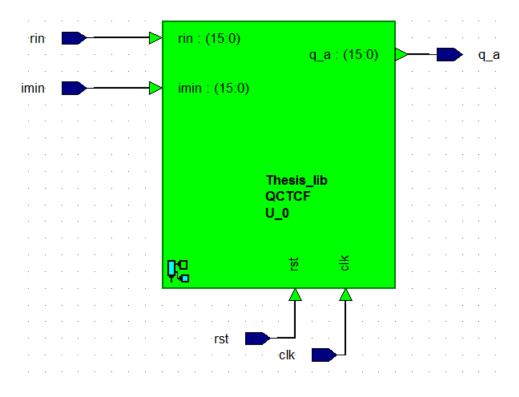

| 5.2    | QCTCF Module                                                  | 63 |

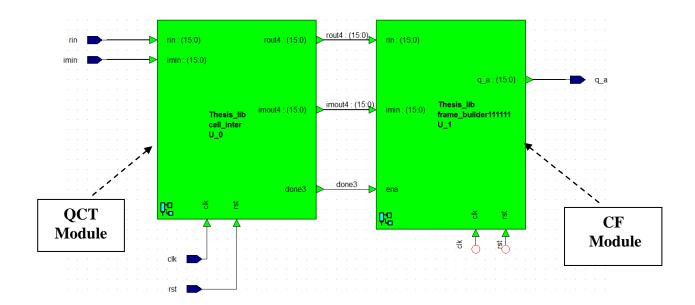

| 5.3    | QCT and CF Module                                             | 64 |

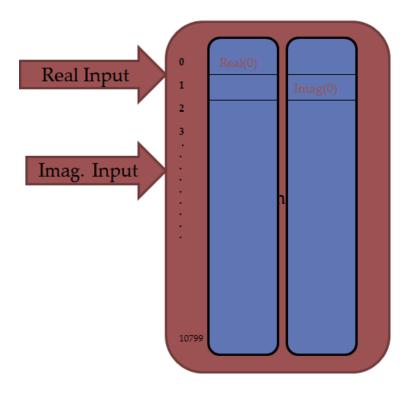

| 5.4    | The data input format for each clock for I and Q components   | 64 |

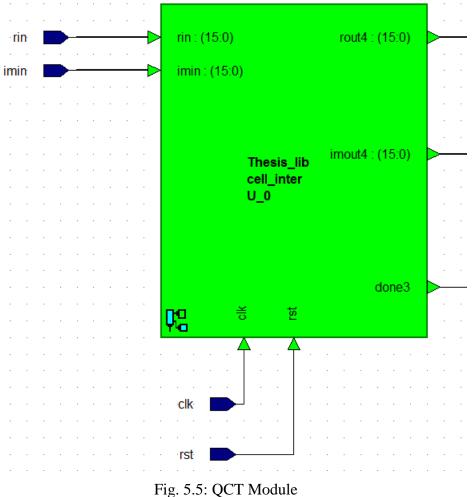

| 5.5    | QCT Module                                                    | 65 |

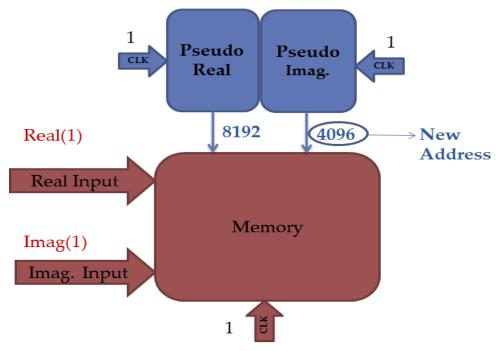

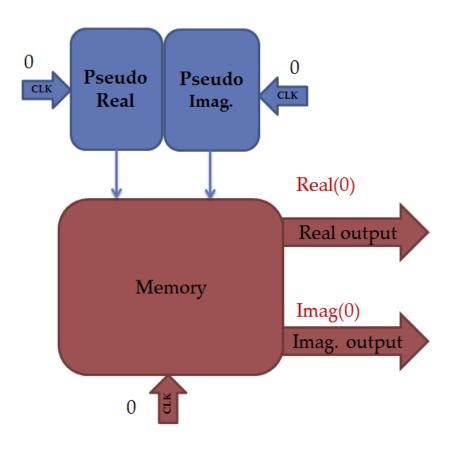

| 5.6(a) | Cyclic Q delay operation for the first clock                  | 66 |

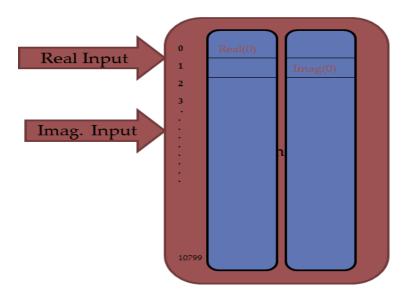

| 5.6(b) | Cyclic Q delay operation for the second clock                 | 66 |

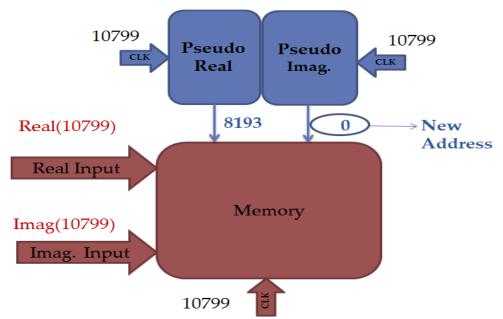

| 5.6(c) | Cyclic Q-delay operation for clock number 10799               | 67 |

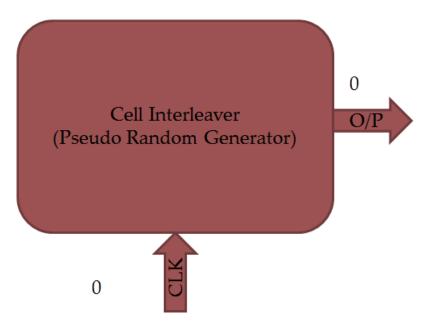

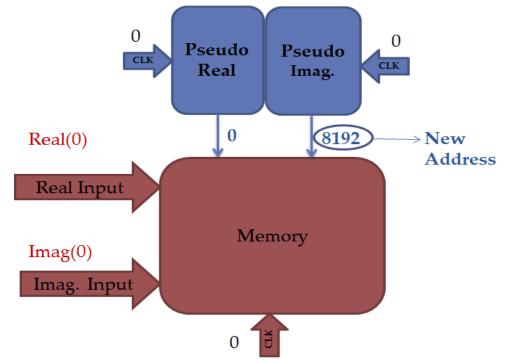

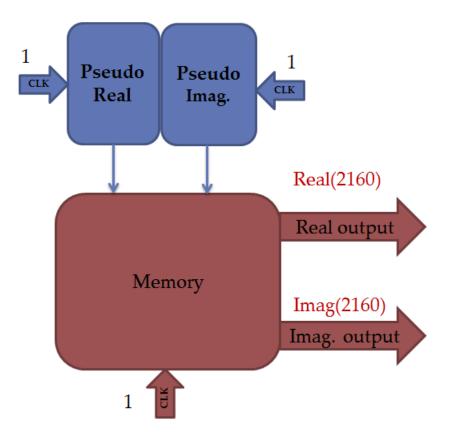

| 5.7(a) | Cell interleaving process for the first clock                 | 68 |

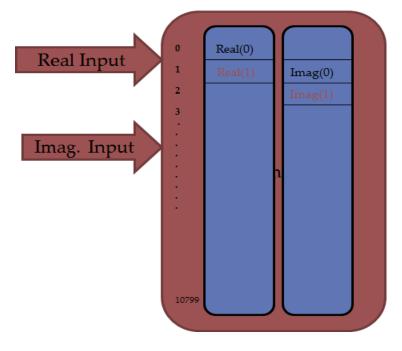

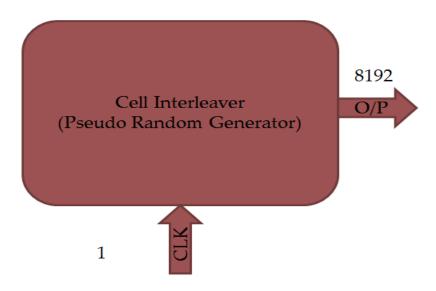

| 5.7(b) | Cell interleaving process for the second clock                | 68 |

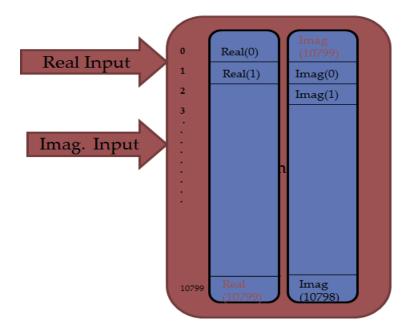

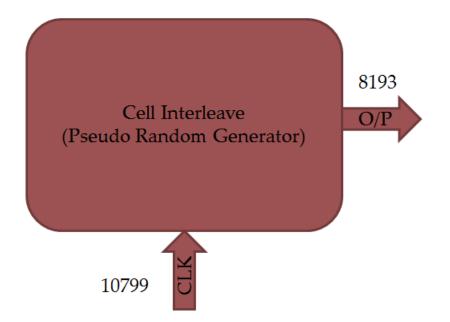

| 5.7(c) | Cell interleaving process for the clock 10799                 | 69 |

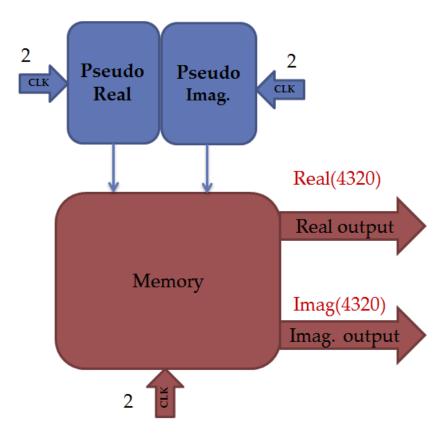

| 5.8(a) | The combined operation for the first clock                    | 69 |

| 5.8(b) | The combined operation for the second clock                   | 70 |

| 5.8(c) | The combined operation for clock number 10799                 | 70 |

| 5.9(a) | The time interleaving operation for the first clock           | 71 |

| 5.9(b)  | The time interleaving operation for the second clock                 | 71 |

|---------|----------------------------------------------------------------------|----|

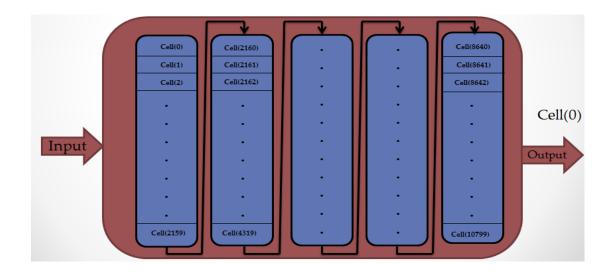

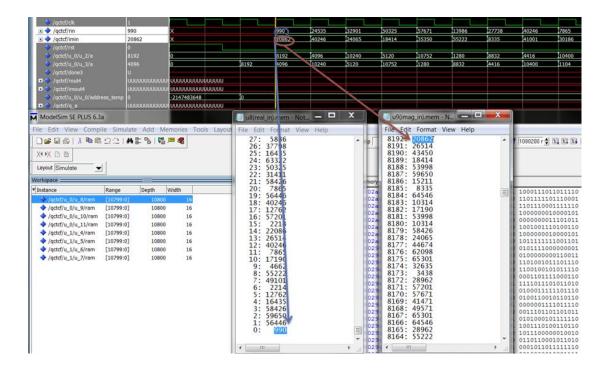

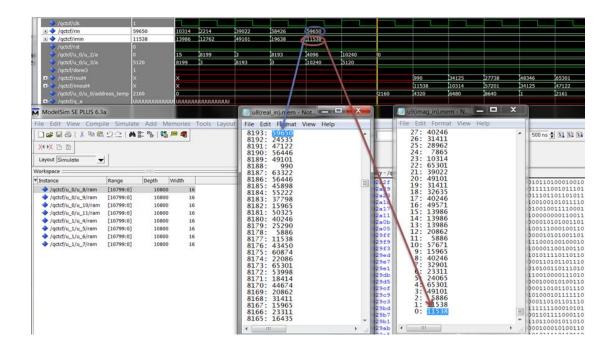

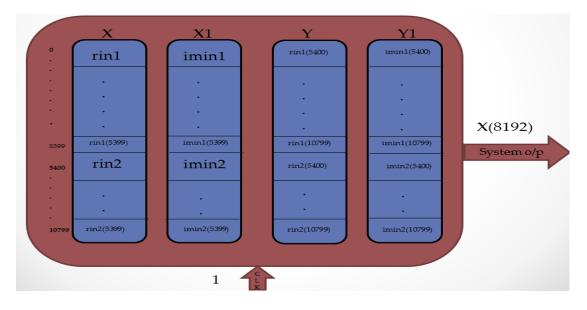

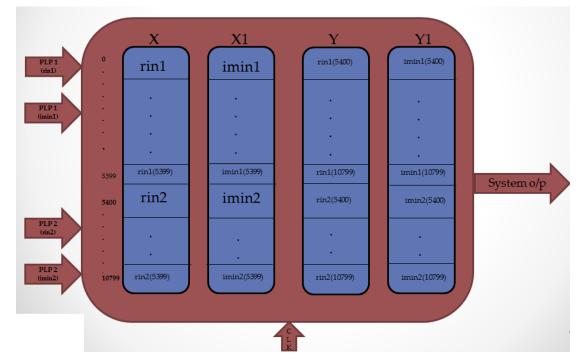

| 5.10(a) | The first QCT module output after 10799 saving clocks                | 72 |

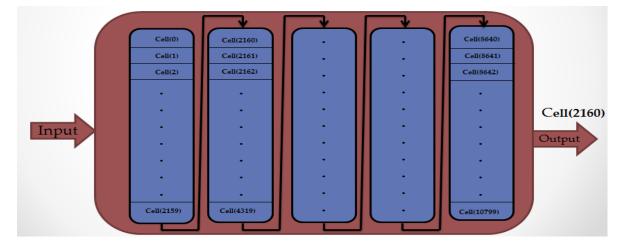

| 5.10(b) | The second QCT module output after 10799 saving clocks               | 73 |

| 5.10(c) | The third QCT module output after 10799 saving clocks                | 73 |

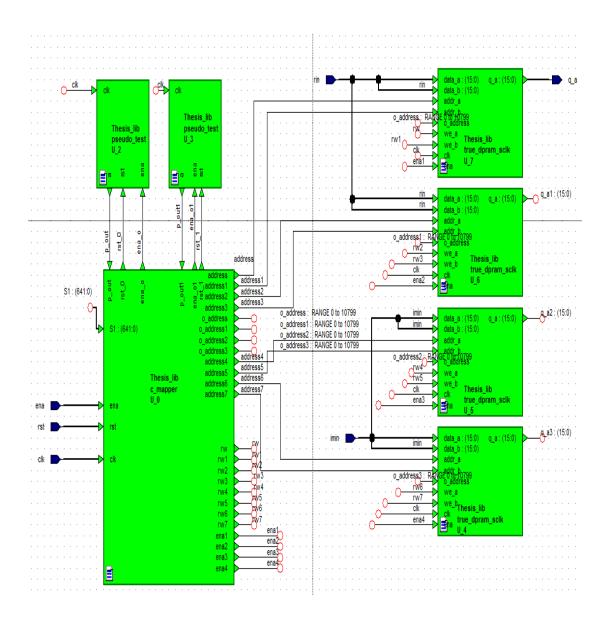

| 5.11    | The internal QCT Module                                              | 74 |

| 5.12(a) | The first 5 inputs to the QCT module                                 | 75 |

| 5.12(b) | The saving operation of cyclic Q delay with cell interleaving        | 76 |

|         | operations of the first input I and Q components                     |    |

| 5.12(c) | The last 5 inputs to the QCT module                                  | 76 |

| 5.12(d) | The saving operation of cyclic Q delay with cell interleaving        | 77 |

|         | operations of the last input I and Q components                      |    |

| 5.12(e) | The time of QCT module produce its first input                       | 77 |

| 5.12(f) | The QCT module output sequence                                       | 78 |

| 5.12(g) | The time of QCT module produce its first input                       | 78 |

| 5.13    | The CF module                                                        | 79 |

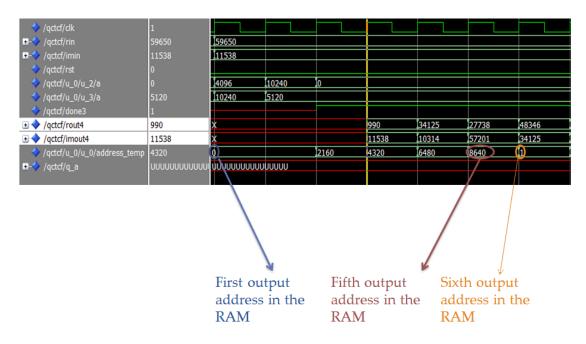

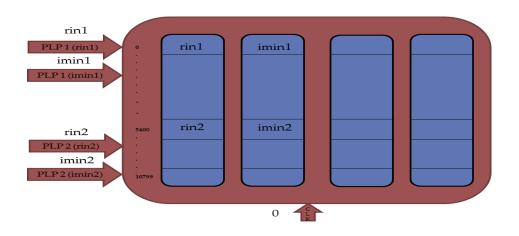

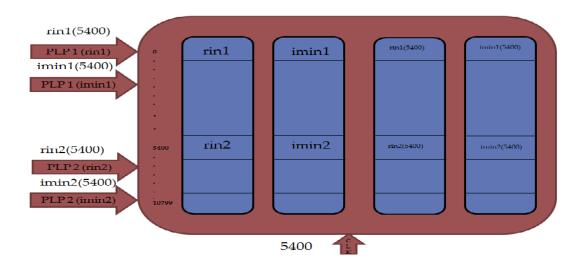

| 5.14(a) | The cell mapper operation of the first clock                         | 80 |

| 5.14(b) | The cell mapper operation of clock number 5400                       | 80 |

| 5.15(a) | The frequency interleaving operation of the first output             | 81 |

| 5.15(b) | The frequency interleaving operation of the second output            | 81 |

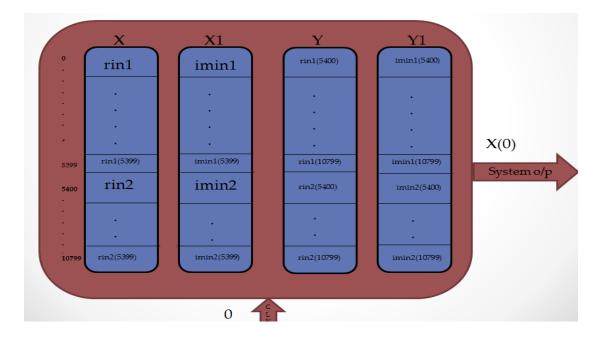

| 5.16    | The combination of cell mapper with frequency interleaver operations | 82 |

| 5.17    | The CF module internally                                             | 83 |

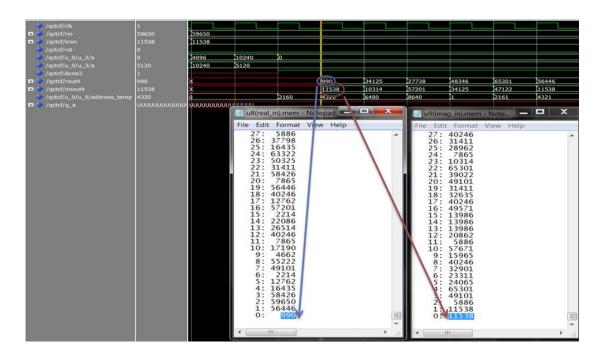

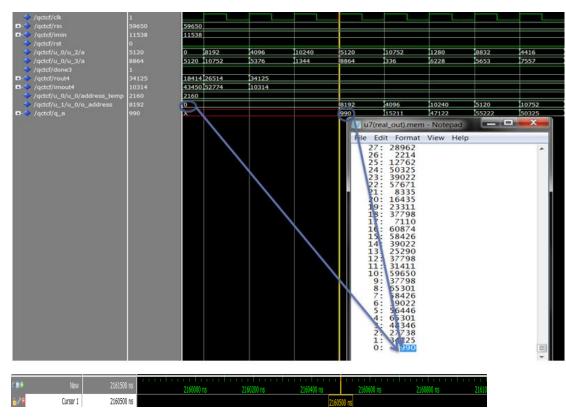

| 5.18(a) | The QCTCF module first output                                        | 84 |

| 5.18(b) | The QCTCF module second output                                       | 85 |

| 5.19    | Simulation of DVB-T2 without using QCTCF module                      | 87 |

| 5.20    | QCTCF Module synthesizing flow summary                               | 88 |

|         |                                                                      |    |

# LIST OF TABLES

xi

| Table  | Caption                                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------------------------------|------|

| 2.1    | DVB-S vs. DVB-S2                                                                                          | 11   |

| 2.2    | The main differences between DVB-C and DVB-C2                                                             | 15   |

| 2.3    | The differences between DVB-T and DVB-T2                                                                  | 19   |

| 3.1    | QLDPC values for normal frames                                                                            | 27   |

| 3.2    | Column twisting parameter tc                                                                              | 28   |

| 3.3    | Number of sub-streams in de-multiplexer                                                                   | 28   |

| 3.4    | Parameters for bit-mapping into constellation                                                             | 29   |

| 3.5    | Rotation angle for each modulation Type                                                                   | 30   |

| 3.6    | The number of time interleaver rows                                                                       | 33   |

| 3.7    | Maximum frame length LF in OFDM symbols for different FFT sizes and guard intervals (for 8 MHz bandwidth) | 35   |

| 3.8    | Number of available data cells in one normal symbol                                                       | 36   |

| 3.9    | Duration of the guard interval for different FFT sizes                                                    | 38   |

| 4.1(a) | The first 10 input cells to the cyclic Q delay module                                                     | 45   |

| 4.1(b) | The last 10 input cells to the cyclic Q delay module                                                      | 45   |

| 4.1(c) | The first 10 cyclic Q delay outputs                                                                       | 45   |

| 4.1(d) | The last 10 cyclic Q delay outputs                                                                        | 45   |

| 4.2(a) | The first 10 pseudo random permutation output counts                                                      | 48   |

| 4.2(b) | The last 10 pseudo random permutation output counts                                                       | 48   |

| 4.2(c) | The first 10 cell interleaver outputs                                                                     | 49   |

| 4.2(d) | The last 10 cell interleaver outputs                                                                      | 49   |

| 4.3(a) | The first 10 time interleaver module output                                                               | 50   |

| 4.3(b) | The last 10 time interleaver module output                                                                | 50   |

| 4.4(a) | The first 10 cell mapper module output                                                                    | 52   |

| 4.4(b) | The last 10 cell mapper module output                                                                     | 52   |

| 4.5(a) | The first 10 time de-interleaver outputs                                                                  | 56   |

| 4.5(b) | The last 10 time de-interleaver outputs                                                                   | 56   |

| 4.6(a) | The first 10 cell de-interleaver outputs                                                                  | 57   |

| 4.6(b) | The last 10 cell de-interleaver outputs                                                                   | 57   |

| 4.7(a) | The first 10 input cells to the cyclic Q delay module                                                     | 58   |

| 4.7(b) | The last 10 input cells to the cyclic Q delay module | 58 |

|--------|------------------------------------------------------|----|

| 5.1    | QCT Matlab output                                    | 79 |

| 5.2    | QCTCF Matlab output                                  | 85 |

# LIST OF PUBLICATIONS

- Hesham A. Fahmy, Safa Gasser, Khaled Shehata, "Combining Cyclic Q Delay and Cell Interleaver for Enhanced Performance DVB-T2 System," 2014 The Society of Digital Information and Wireless Communications (SDIWC), Prague Czech Republic (Published)

- Hesham A. Fahmy, Safa Gasser, Khaled Shehata "Efficient Hardware Implementation of DVB-T2 Combined Modules" *Electronics Letters* (To Be Submitted)

# **CHAPTER 1**

## **INTRODUCTION**

#### **1.1 Introduction**

The analog to digital video broadcasting conversion started to take place gradually with the birth of the ISDB (Integrated Services Digital Broadcasting), ATSC (Advanced Television Systems Committee) and Digital Video Broadcasting (DVB) organizations.

DVB-T which is a standard for digital terrestrial television broadcast transmission is first published in 1997 and was firstly used in Sweden and UK in1998. The DVB-T standard is the most successful digital terrestrial television standards in the world [1]. Since the publication of the DVB-T standard, however research in transmission technology has continued.

The second generation DVB standard aims to replace the current standard DVB-T or to enter the new market in the countries where analogue to digital TV is not been introduced [2], [3].

### 1.2 General Background

In the past few years, there has been a tremendous amount of research in the DVB-T2 area. The main motivation of digital broadcasting is to provide broadcasters with more advanced, efficient over analog in the regard of bandwidth efficiency, robustness improvement against propagation, as well as reception stability.

For the DVB-T2 system simulation, the authors in [4], [5] proposed a new error correction techniques which is a combination of both LDPC (Low density Parity Check) and BCH (Bose-Chaudhuri-Hocquengham) employed in DVB-T2. The combination technique was aimed to replace the traditional convolutional and Reed Solomon coding employed in DVB-T. In [6], [7] the authors mainly focused on researching, simulating and testing the BICM (Block Interleaving and Coding

Modulation) block in the DVB-T2 system. In their simulation and testing the authors included all possible interleaving, coding and modulation present in any BICM block carried out on a single PLP (Physical Layer Pipe). In [8] the Constellation rotation technique was analysed which is one of the features employed DVB-T2 system. The constellation rotation is known to increases system robustness. DVB-T2 standard includes two methods for PAPR (Peak to Average Power Ratio) reduction techniques which are ACE (Active Constellation Extension) and TR (Tone Reservation). The two techniques adopted for PAPR in DVB-T2 system are investigated in details in [9], [10].

For the system implementation, the implementation guidelines are illustrated in [11]. The authors in [12] designed and developed forward error correction (FEC) part for better performance DVB-T2. In [13], [14] they designed the rotated QAM Mapper/De-mapper for the DVB-T2 Standard. The authors in [15] started to design the DVB-T2 modulator modules supporting multiple PLP. In [16], [17], [18] the authors start to create new algorithms for increasing BICM performance.

#### **1.3 Research Objective and Thesis Outline**

In this research, we implement an efficient integrated hardware module that combines cyclic Q delay, cell interleaver, time interleaver, cell mapper and frequency interleaver modules for the DVB-T2 system transmitter. As a preliminary step and for verification purposes we write a Matlab program for the combined modules and then we write a VHDL code. Comparing the results of both programs is the following step. Finally synthesizing is applied using Quartus 11.2 program to check that the module is synthesizable.

Thus, this thesis is organized as follows:

**Chapter 2** we give a brief overview of digital television and its related standards which are ATSC, ISDB and DVB. Afterwards the DVB system is discussed showing the basic DVB block diagram. Finally, the different standards of the DVB are mentioned briefly indicating the similarities and differences between them.

**Chapter 3** we introduce the DVB-T2 system (transmitter and receiver). The system's principal features and key technologies are mentioned such as error protection, mapping, modulations, and interleaving. The algorithm of every block within the system is fully discussed.

**Chapter 4** we present the Matlab simulation of the cyclic Q delay, cell interleaver, time interleaver, cell mapper and frequency interleaver modules of the DVB-T2 system in transmitter and receiver.

**Chapter 5** we show the hardware implementation steps of these five modules. A VHDL program is written for every module using the FPGA Adv.Pro 8.1 program. Synthesizing is then applied showing complexity and processing time speed using Quartus 11.2.

**Chapter 6** we conclude our work and also this chapter contains the future work to be done on the DVB-T2 system.

# **CHAPTER 2**

### DIGITAL VIDEO BROADCASTING

#### 2.1 Introduction

Digital television (DTV) has become the world's very exciting topic in the television broadcasting through years. DTV along with high definition television (HDTV) services empowered by advanced digital broadcasting technologies the viewers to have the excellent watching experience with respect to the analog TV.

Thus, this chapter is divided into two sections. In section one, the different widely used digital television terrestrial broadcasting standards (DTTB) are mentioned briefly. In section two, we introduce the different DVB standards like DVB-T, DVB-T2, DVB-C and DVB-C2, focusing on the similarities and differences between them.

#### **2.2 Digital Television Standards**

#### 2.2.1 Advanced Television System Committee (ATSC)

The Advanced Television Systems Committee (ATSC) is a standards organization created in 1982 as part of the Advanced Television Committee (ATV) [19]. The ATSC is created to promote the establishment of technical standards for all aspects of advanced television systems. ATSC has grown from 25 original organizational members to an international membership of over 200, including broadcasters, motion picture companies, telecommunications carriers, cable TV programmers, consumer electronics manufacturers, and computer hardware and software companies.

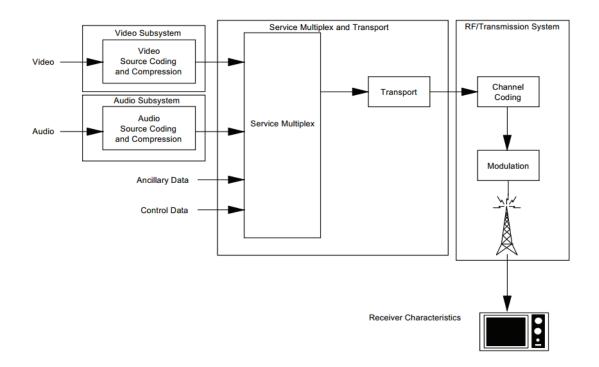

The ATSC signals are designed to use the same 6 MHz bandwidth as analog NTSC television channels. Figure 2.1 shows the ATSC block diagram. The system consists of three main parts: Video Subsystem (or audio subsystem), Service Multiplex and Transport system and RF/Transmission System.

The Digital Television Standard is the system used to transmit high quality video and audio and ancillary data over a single 6 MHz channel. This means that encoding a video source whose resolution can be as high as five times that of conventional television (NTSC) resolution requires a bit rate reduction by a factor of 50 or higher. To achieve this reduction, the system is designed to be efficient in utilizing available channel capacity by exploiting complex video and audio compression technology. The objective is to maximize the information passed through the data channel by minimizing the amount of data required to represent it.

Fig. 2.1: ATSC Block Diagram [19]

The "Source coding and compression" refers to the bit rate reduction methods. The purpose of the coder is to minimize the number of bits needed to represent the audio and video information. On the other hand the "Service multiplex and transport" is a means of dividing the digital data stream into packets of information. The digital television system employs the MPEG-2 transport stream syntax for the packetization and multiplexing video, audio and data signals compression. The MPEG-2 transport stream syntax is used in applications where channel bandwidth or recording media capacity is limited. The "RF/transmission" block refers to channel coding and modulation. The channel coder takes the data bit stream and adds additional information that is used by the receiver to reconstruct the data from the received signal which, due to transmission, may not be represented accurately from the transmitted signal.

#### **2.2.2 Integrated Services Digital Broadcasting (ISDB)**

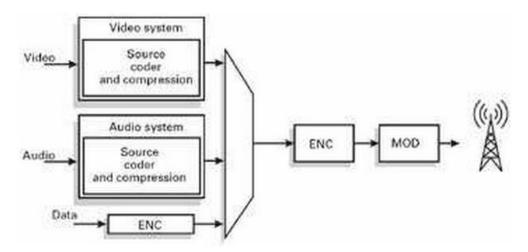

The Integrated Services Digital Broadcasting (ISDB) is a Japanese standard for digital television (DTV) and digital radio (DAB). Figure 2.2 shows the block diagram of the ISDB system.

Fig 2.2 ISDB Block Diagram [20]

The ISDB is divided into three different types of systems; ISDB-C (Cable), ISDB-S (Satellite) and ISDB-T (Terrestrial) [20]. They are developed to provide expandability, flexibility and multimedia broadcasting commonality. MPEG2-TS (transport streams) can be handled by the system by employing a frame structure.

Besides audio and video transmission, ISDB also defines data connections (Data broadcasting) with the internet as a return channel over several media (10Base-T/100Base-T, Telephone line modem, Mobile phone, Wireless LAN (IEEE 802.11) etc.) and with different protocols. This is used, for example, for interactive interfaces like data broadcasting (ARIB STD-B24) and electronic program guides (EPG).

#### 2.2.3 Digital Video Broadcasting (DVB)

The DVB project is an industry led consortium of over 270 television broadcasting associated companies world-wide. The DVB is being adopted as the standard for digital television in many countries. The committee structure of the project was committed to design an open interoperable technical standard for the global delivery of digital media and broadcast services.

The DVB system's three key standards and most commonly used standards were DVB-S for satellite networks, DVB-C for cable networks and DVB-T for terrestrial networks for data distribution. DVB then moved to embrace network convergence through the development of standards using innovative technologies that allow the delivery of DVB services over fixed and wireless telecommunications networks (e.g. DVB-H and DVB-SH for mobile TV). 2009 saw the completion of the family of second generation delivery standards; with DVB-T2 (terrestrial) and DVB-C2 (cable) joining the already published and deployed DVB-S2 (satellite). These distribution systems differ mainly in the modulation schemes used and error correcting codes used, due to the different technical constraints [21].

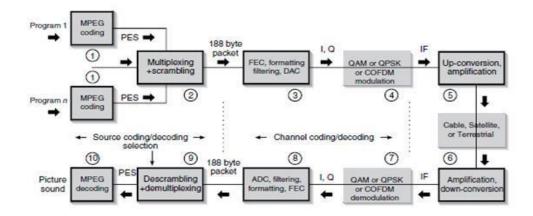

Fig. 2.3: DVB Block Diagram [21]

The basic block diagram of all DVB system is shown in figure 2.3. The system starts with a source encoder which is one of the MPEG families. The DVB-T standard uses MPEG2 while DVB-T2 uses MPEG4. The MPEG passes the video and audio packets of the programs through the multiplexer. The multiplexer uses the input packets to form 188 byte transport packets, which are eventually scrambled. After the data is packetized, it passes through a forward error correction technique (channel coding).

To increase the coding efficiency all standards use a concatenation of two encoders. The data is then mapped producing the in-phase (I) and quadrature (Q) signals. The DVB-S standard uses the QPSK scheme while the DVB-T uses the QAM (cable) or COFDM (terrestrial) and IF carrier (intermediate frequency of the order of 70 MHz). This IF carrier is then up-converted into the appropriate frequency band (depending on the medium) for transmission to the end users.

#### **2.3 Different DVB Standards**

#### 2.3.1 Digital Video Broadcasting- Satellite (DVB-S)

The DVB-S is an abbreviation for Digital Video Broadcasting — Satellite. It was first introduced in 1993. At its core, DVB-S is a simple mechanism. Digital transmitters beam sets of channels to an area, and they are received by antennas aimed at the transmitter [22].

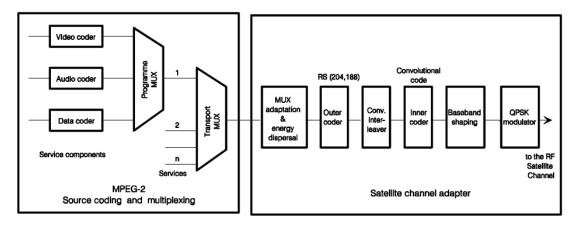

Fig.2.4: DVB-S Block Diagram [22]

The DVB-S is used in both Multiple Channel Per Carrier (MCPC) and Single channel per carrier modes for Broadcast Network feeds as well as for Direct Broadcast Satellite services.

The DVB-S system is based on QPSK modulation and convolutional forward error correction (FEC), concatenated with Reed–Solomon coding.

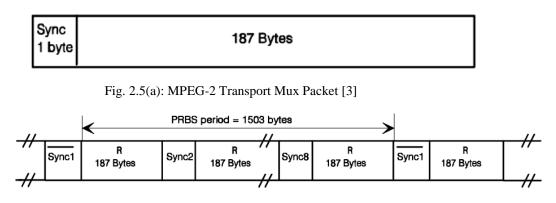

Figure 2.4 illustrates the block diagram of DVB-S. The System is directly compatible with MPEG-2 coded TV signals. The total packet length of the MPEG-2 transport Multiplex (MUX) packet is 188 bytes as shown in figure 2.5(a). The data of the input MPEG-2 multiplex is then randomized [22], in order to comply with ITU Radio Regulations. The data stream passes through the Reed Solomon encoder as a first step of encoding. Reed-Solomon RS shortened code, from the original RS code, is applied to each randomized transport packet (188 bytes) of figure 2.5(b) to generate an error protected packet as in figure 2.5(c).

Fig. 2.5(b): Randomized Transport Packets [3]

Fig. 2.5(c): (204, 188, 8) Reed Solomon error protected packets [22]

The data stream passes through the convolutional interleaving process which is based on the Forney approach. The interleaved frame is composed of overlapping error protected packets and is delimited by inverted or non-inverted MPEG-2.

After the interleaving stage the data stream passes through punctured convolutional codes. This allows selection of the most appropriate level of error correction for a given service or data rate. The System shall allow convolutional coding with code rates of 1/2, 2/3, 3/4, 5/6 and 7/8 [22].

# 2.3.2 Digital Video Broadcasting- Satellite Second Generation (DVB- S2)

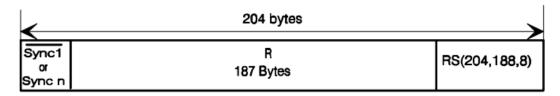

The DVB-S2 stands for digital video broadcasting-satellite second generation. The standard is developed in 2003 by the DVB Project and ratified by ETSI in March 2005 [24]. DVB-S2 Standard represents a major step forward compared to the DVB-S one.

Figure 2.6 represents the DVB-S2 block diagram. DVB-S2 is based on a Forward Error Correction technique of BCH encoder and LDPC encoder concatenated. Furthermore, the standard encompasses a wide range of coding rates and modulation formats to achieve the best performance-complexity trade-off. DVB-S2 benefits from more recent developments in channel coding and modulation. It uses QPSK, 8PSK, 16APSK and 32APSK. The result is typically a 30 % capacity increase

over DVB-S under the same transmission conditions. This enables DVB-S2 to operate over a signal-to-noise range exceeding 18 dB exceeding by far the QPSK based DVB-S operating range which is restricted to less than 5 dB. Table 2.1 gives a comparison between both DVB-S and DVB-S2 systems.

Fig.2.6: DVB-S2 Block Diagram [22]

|              | DVB-S                             | DVB-S2                                                               |

|--------------|-----------------------------------|----------------------------------------------------------------------|

| Input        | Single Transport Stream           | Multiple Transport Stream and                                        |

| Interface    | (TS)                              | Generic Stream (GSE)                                                 |

| Modes        | Constant Coding and<br>Modulation | Variable Coding and Modulation<br>and Adaptive Coding and Modulation |

|              |                                   | 1 0                                                                  |

| FEC          | Reed Solomon (RS)                 | LDPC + BCH                                                           |

|              | 1/2,2/3,3/4,5/6,7/8               | 1/4,1/3,2/5,1/2,3/5,2/3,3/4,4/5,                                     |

|              |                                   | 5/6,8/9,9/10                                                         |

| Modulation   | Single Carrier                    | Single Carrier QPSK with Multiple                                    |

|              | QPSK                              | Streams                                                              |

| Modulation   | BPSK,QPSK,                        | BPSK,QPSK, 8PSK,                                                     |

| Schemes      | 8PSK, 16QAM                       | 16APSK,32APSK                                                        |

| Interleaving | Bit-Interleaving                  | Bit-Interleaving                                                     |

| Pilots       | Not Applicable                    | Pilot Symbols                                                        |

Table 2.1: DVB-S vs. DVB-S2

#### 2.3.3 Digital Video Broadcasting-Cable (DVB-C)

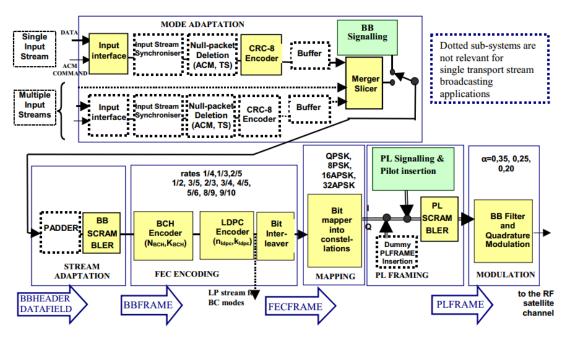

DVB-C stands for Digital Video Broadcasting-Cable. The standard was first published by the ETSI in 1994, and subsequently became the most widely used transmission system for digital cable television in Europe. Figure 2.7 shows the DVB-C block diagram. The DVB-C transmitter is similar to the DVB-S standard transmitter in most of its stages [25].

Figure 2.7: DVB-C Block Diagram [25]

The operation starts when video, audio, and data streams are multiplexed into MPEG-2 transport stream. The MPEG-TS is identified as a sequence of data packets, of fixed length (188 bytes). A first level of protection is then applied to the transmitted data, using a non-binary block code, a Reed-Solomon RS (204, 188) code, allowing the correction of up to a maximum of 8 wrong bytes for each 188-byte packet.

The data sequence passes through the external interleaver, where a convolutional interleaving is used to rearrange the transmitted data sequence, such that it becomes more rugged to long sequences of errors. After that data bytes faces the Byte/m-tuple conversion block so that the data bytes are encoded into bit m-tuples (m = 4, 5, 6, 7, or 8).

In order to get a rotation-invariant constellation, the data passes through Differential coding unit. This unit applies a differential encoding of the two Most Significant Bits of each symbol. Then the bit sequence is mapped into a base-band digital sequence of complex symbols. The system allows five modulation modes: 16-QAM, 32-QAM, 64-QAM, 128-QAM, 256-QAM. Then in order to remove mutual signal interference at the receiving side, base-band shaping block is employed, where the QAM signal is filtered with a raised-cosine shaped filter.

Finally, the digital signal is transformed into an analog signal, with a digitalto-analog converter (DAC), and then modulated to radio frequency by the RF frontend.

#### 2.3.4 Digital Video Broadcasting-Cable Second Generation (DVB-C2)

DVB-C2 stands for Digital Video Broadcasting- Cable Second generation. The final DVB-C2 specification was approved by the DVB Steering Board in April 2009. Figure 2.8 shows the DVB-C2 transmitter. The DVB-C2 transmitter is similar to the DVB-T2 standard transmitter in most of its stages.

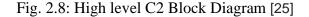

Fig. 2.9(a): Mode adaptation for single input stream (PLP) [25]

Fig. 2.9(b): Bit Interleaved Coding and Modulation (BICM) [25]

Fig. 2.9(c): Data Slice + Frame builder [25]

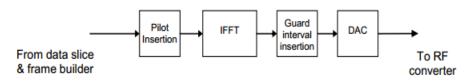

Fig. 2.9(d): OFDM Generation [25]

The input to the transmitter consists of one or more logical data streams [26]. These data streams are carried by Physical Layer Pipes (PLP). DVB-C2 uses the same Forward Error correction technique as DVB-T2 which is a concatenation of two encoders, a LDPC encoder and a BCH encoder. Then the data is interleaved, coded and modulated through the BICM stage as shown in figure 2.9(b). Each stream is demultiplexed into N sub-streams. These N sub-streams pass through a cell mapper using a Quadrature Amplitude Modulation Scheme. The OFDM generation is the last stage which is a very simple OFDM transmitter as in figure 2.9(d) illustrates.

DVB-C2 offers greater than 30% higher spectrum efficiency under the same conditions compared to DVB-C standard, and the gains in downstream channel capacity is greater than 60% for optimized HFC networks. DVB-C2 allows bitrates up to 83.1 Mbit/s on an 8 MHz channel bandwidth when using 4096-QAM modulation;

future extensions allow up to 97 Mbit/s and 110.8 Mbit/s per channel using 64QAM and 265AQAM modulation. Table 2.2 summarizes the main differences between DVB-C and DVB-C2.

|                 | DVB-C                   | DVB-C2                        |

|-----------------|-------------------------|-------------------------------|

| Input Interface | Single Transport Stream | Multiple Transport Stream and |

|                 | (TS)                    | Generic Stream (GSE)          |

| Modes           | Constant Coding         | Variable Coding and           |

|                 | and Modulation          | Modulation and Adaptive       |

|                 |                         | Coding and Modulation         |

| FEC             | Reed Solomon (RS)       | LDPC + BCH                    |

|                 | 1/2,2/3,3/4,5/6,7/8     | 1/2, 2/3,3/4,4/5,5/6,8/9,9/10 |

| Modulation      | Single Carrier          | Absolute                      |

|                 | QAM                     | OFDM                          |

| Modulation      | 16- to 256-             | 16-to 4096-                   |

| Schemes         | QAM                     | QAM                           |

| Interleaving    | Bit-Interleaving        | Bit-Time and Frequency        |

|                 |                         | Interleaving                  |

| Pilots          | Not Applicable          | Scattered and Continual       |

Table 2.2: The main differences between DVB-C and DVB-C2

### 2.3.5 Digital Video Broadcasting-Handheld (DVB-H)

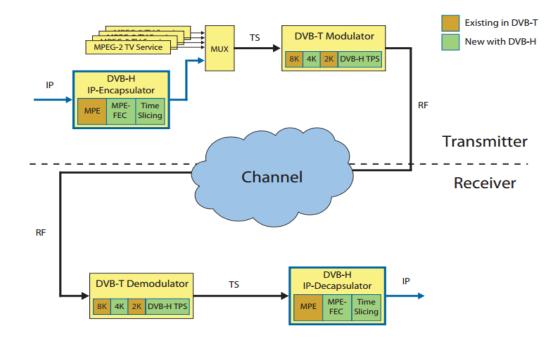

DVB-H stands for Digital Video Broadcasting- Handheld. DVB-H standard is formally adopted as ETSI standard in November 2004. Figure 2.10 shows the DVB-H block diagram. DVB-H technology is a superset of the successful DVB-T system, with additional features to meet the specific requirements of handheld, batterypowered receivers.

Figure 2.10: Additions brought to the DVB-T system by DVB-H [27]

DVB-H is a physical layer specification designed to enable the efficient delivery of IP-encapsulated data over terrestrial networks. DVB-H present four main requirements: broadcast services for portable and mobile usage with acceptable quality; a typical user environment, and so geographical coverage, as mobile radio; access to service while moving in a vehicle at high speed; and as much compatibility with existing (DVB-T), to allow sharing of network and transmission equipment [27].

DVB-H uses a mechanism called multi-protocol encapsulation (MPE), making it possible to transport data network protocols on top of MPEG-2 transport streams. A forward error correction (FEC) scheme is used in conjunction with this multi-protocol to improve the robustness and thus mobility of the signal. In addition to the 2k and 8k modes available in DVB-T, a 4k mode is added to DVB-H increasing the network design flexibility. A short in-depth interleaving process is introduced for 2k and 4k modes that lead to better tolerance against impulsive noise. DVB-H uses Time slicing technology to reduce power consumption for small handheld terminals.

#### **2.3.6 Digital Video Broadcasting – Terrestrial (DVB- T)**

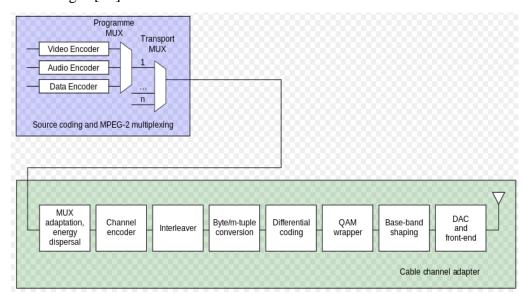

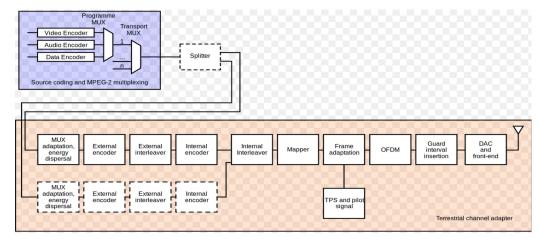

DVB-T (Digital Video Broadcasting-Terrestrial) which is a standard for digital terrestrial television broadcast is first published in 1997. It is first used in Sweden and UK in1998. Figure 2.11 shows the DVB-T system. The main key is to transmit digital signal to offer high definition television services as efficiently and effectively as possible.

Fig. 2.11: DVB-T Block Diagram [28]

DVB-T system transmits compressed digital audio, digital video and other data in an MPEG transport stream, using coded orthogonal frequency-division multiplexing (COFDM or OFDM) modulation. There are three valid modulation schemes: QPSK, 16-QAM, 64-QAM adopted by the DVB-T [28].

The DVB-T process starts with compressed video, compressed audio, and data streams then multiplexed into an MPEG program streams (MPEG-PSs) using Source coding and MPEG-2 multiplexing (MUX) block. The resulting data stream passes through splitter where the two different MPEG-TSs are transmitted at the same time, using a technique called Hierarchical Transmission.

A first level of error correction is applied to the transmitted data, using a nonbinary block code, a Reed-Solomon RS (204, 188) code, allowing the correction of up to a maximum of 8 wrong bytes for each 188-byte packet using an external encoder. The data coming out of the external encoder are then interleaved by convolutional interleaver. It is used to rearrange the transmitted data sequence.

A second level of error correction is done by the means of convolutional code used as internal encoder. The data sequence is rearranged again through an internal interleaver, aiming to reduce the effect of burst errors. The digital bit sequence is mapped into a base band modulated sequence of complex symbols. The complex symbols are grouped into blocks of constant length (1512, 3024, or 6048 symbols per block). A frame is generated, 68 blocks long, and a superframe is built by 4 frames. Pilot signals are used during the synchronization and equalization phase. In order to simplify the reception of the signal being transmitted on the terrestrial radio channel, additional signals (Guard intervals) are inserted in each block. The sequence of blocks is modulated according to the OFDM technique (2k or 8k mode).

Finally, the digital signal is transformed into an analogue signal, by the means of a digital-to-analogue converter (DAC), and then modulated to radio frequency.

# **2.3.7 Digital Video Broadcasting – Terrestrial Second Generation** (DVB- T2)

DVB-T2 (The second generation DVB) standard is mainly aimed to replace the current standard DVB-T. The DVB-T2 is standardized by ETSI in September 2009. The DVB-T2 is a redefined system that allows a more efficient usage substituting the extremely large DVB-T cost. The main motivation of DVB-T2 is to provide broadcasters with more advanced and efficient alternative to DVB-T standards.

The DVB-T2 system introduces a new modulation and coding techniques in comparison with DVB-T. In addition, the standard range of COFDM (Coded Orthogonal Frequency Division Multiplexing) parameters has been extended with respect to DVB-T in order to provide a greater flexibility [29].

A new error correction technique which is a combination of both LDPC (Low density Parity Check) and BCH (Bose-Chaudhuri-Hocquengham) is employed in the DVB-T2 system, aimed to replace the traditional convolutional and Reed Solomon coding employed in DVB-T.

DVB-T2 system supports different types of mapping schemes as QPSK, 16QAM, 64QAM and 256QAM. For better performance the constellations rotation and cyclic Q delay are used to uncorrelate between the in-phase and quadrature components.

DVB-T2 standard includes two new methods for PAPR (Peak to Average Power Ratio) reduction techniques, which are ACE (Active Constellation Extension) and TR (Tone Reservation) with respect to DVB-T standard. Table 2.3 gives a summary of comparison between the DVB-T and the DVB-T2 systems.

|                       | DVB-T                                                             | DVB-T2                                         |

|-----------------------|-------------------------------------------------------------------|------------------------------------------------|

| Input stream          | Single stream                                                     | Multiple stream                                |

| Coding and Modulation | Constant                                                          | Variable                                       |

| FEC                   | Convolutional coding + Reed<br>Solomon<br>1/2, 2/3, 3/4, 5/6, 7/8 | LDPC + BCH<br>1/2, 3/5, 2/3, 3/4, 4/5, 5/6     |

| Modulation<br>Schemes | QPSK, 16QAM, 64QAM                                                | QPSK, 16QAM,<br>64QAM, 256QAM                  |

| Modulation            | OFDM                                                              | OFDM                                           |

| Guard<br>Interval     | 1/4, 1/8,<br>1/16, 1/32                                           | 1/4, 19/256, 1/8, 19/128,<br>1/16, 1/32, 1/128 |

| Scattered Pilots      | 8% of total                                                       | 1%, 2%, 4%, 8% of total                        |

| Continual Pilots      | 2.6% of total                                                     | 0.35% of total                                 |

| DFT                   | 2k, 8k                                                            | 1k, 2k, 4k, 8k, 16k, 32k                       |

Table.2.3: The differences between DVB-T and DVB-T2

### **2.4 Conclusion**

As a conclusion this chapter covers the different digital television standards in the world like ATSC, ISDB, and DVB. In addition to each standard operation. Finally, the different DVB standards were overviewed along with the similarities and differences between them.

# **CHAPTER 3**

# **DVB-T2** System

### **3.1 Introduction**

In this chapter, we discuss the details of the DVB-T2 system specifications. Thus, this chapter is divided into two main sections. In the first section, we introduce the DVB-T2 standards. The discussion of this section is based on the DVB-T2 standard book. We discuss in details the functions of each block in the transmitter separately. In the second section, we briefly discuss the DVB-T2 receiver as it is considered the inverse of the transmitting process.

## **3.2 DVB-T2 transmitter**

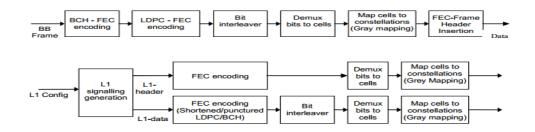

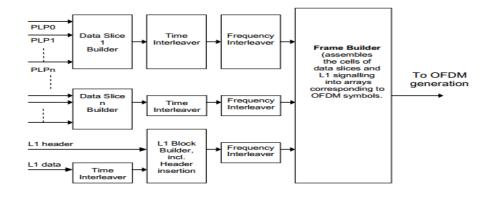

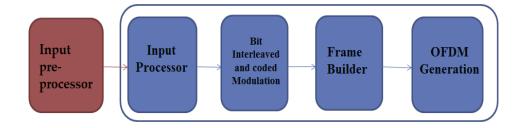

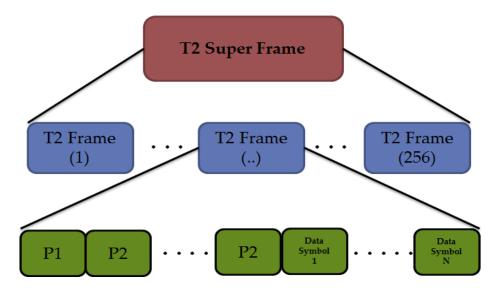

The DVB-T2 transmitter consists of four main blocks: Input processing, Bit interleaved coding and modulation (BICM), Frame builder, and OFDM generation

blocks as shown in the high level architecture of the transmitter figure 3.1. The input preprocessor which is not part of the T2 system includes a Service splitter or demultiplexer for Transport Streams (TS) used in separating the services into the T2 system inputs. The preprocessor output is then carried in individual Physical Layer Pipes (PLPs). Figure 3.2 is the detailed DVB-T2 system architecture.

Fig.3.1: High level T2 block diagram

Fig. 3.2: DVB-T2 Block diagram

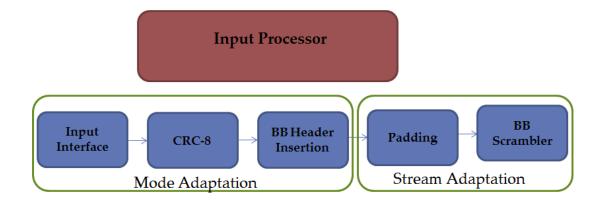

#### 3.2.1 Input processor

The input processing block performs two functions as figure 3.3 shows. The first function is the mode adaptation whereas the second function is the stream adaptation.

Fig.3.3: Input Processor

### **3.2.1.1 Mode Adaptation**

The mode adaptation operates separately on the contents of each PLP. It slices the input data stream into data fields. This data field after stream adaptation will form baseband frames (BBFRAMEs).

The first block of the mode adaptation function is the Input Interface block. The input interface subsystem maps the input into internal logical-bit format. The first received bit is defined as the Most Significant Bit (MSB). The input interface reads a data field, composed of DFL bits (Data Field Length) with the condition of:

$0 < DFL < K_{BCH}$

where, KBCH is the number of bits protected by the BCH encoder.

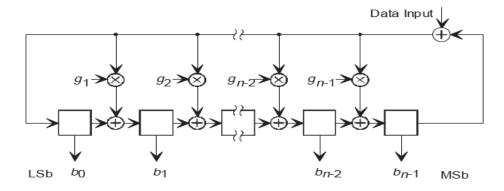

The second block of the mode adaptation module is the Cyclic Redundancy Check (CRC-8) block. It is an error-detecting code commonly used in digital networks and storage devices to detect accidental changes to raw data. Blocks of data entering the CRC encoder get a short check value attached, based on the remainder of a polynomial division of their contents; on retrieval the calculation is repeated, and corrective action can be taken against presumed data corruption if the check values do not match. The systematic cyclic codes are used to encode messages by adding a fixed-length check value, for the purpose of error detection in communication networks. Cyclic codes are very simple to be implemented and they are well suited for the detection of burst errors. This is important because burst errors are common transmission errors in many communication channels, including magnetic and optical storage devices.

The CRC calculation is performed by means of a shift register containing n register stages, equivalent to the degree of the polynomial as figure 3.4 shows. The stages are denoted by b0 to bn. For CRC-8, the polynomial is  $(g0 + g1 \dots + gn-1)$  [29].

Fig. 3.4: CRC Algorithm [29]

The last block of the mode adaptation function is the Baseband header (BBheader) block. The term header refers to supplemental data placed at the beginning of a block of data being stored or transmitted. The DVB-T2 system uses a fixed length BB HEADER of 10 bytes. This header is inserted in front of the baseband data field in order to describe the format of the data field. The BB HEADER takes one of two forms: normal mode (NM) as shown in figure 3.5 (a) or high efficiency mode (HEM) as shown in figure 3.5 (b).

In the header, the input stream format and the type of Mode Adaptation is given in the MATYPE part, while the user packet length and the data field length are given in UPL and DFL parts. A copy of the User Packet Sync-byte is given in the Sync part. The distance in bits from the beginning of the DATA FIELD to the beginning of the first transmitted UP which starts in the data field is given in the SYNCD part. The CRC-8 MODE is the XOR of the CRC-8 (1-byte) field with the MODE field (1-byte). The result of the XOR process indicates the mode used, that is if the result OD then it indicates that we have normal mode while on the other hand if the result is 1D it indicates that we have high efficiency mode [29]. ISSYI (1 bit), (Input Stream Synchronization Indicator) is active when it contains one.

| MATYPE<br>(2 bytes) | UPL<br>(2 bytes)       | DFL<br>(2 bytes) | SYNC<br>(1 byte)         | SYNCD<br>(2 bytes) | CRC-8<br>MODE<br>(1 byte) | (a) |

|---------------------|------------------------|------------------|--------------------------|--------------------|---------------------------|-----|

| MATYPE<br>(2 bytes) | ISSY 2MSB<br>(2 bytes) | DFL<br>(2 bytes) | ISSY<br>1LSB<br>(1 byte) | SYNCD<br>(2 bytes) | CRC-8<br>MODE<br>(1 byte) | (b) |

Fig. 3.5: (a) NM header format, (b) HEM header format [29]

### 3.2.1.2 Stream Adaptation

The first block of the stream adaptation is the Padding block. Padding is adding zeros at the beginning of the data or at the end. It is an optional feature in many communication systems. Padding does not affect the data when added. It is applied in circumstances when the user data available for transmission is not sufficient to completely fill a BBFRAME. The resulting BBFRAME after the padding operation is of a constant length of KBCH bits.

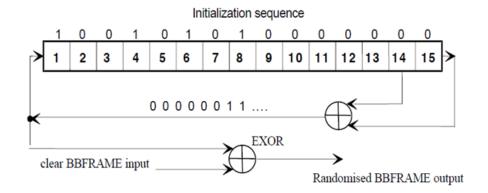

The second block of the stream adaptation is the BB scrambler block. In telecommunications, scrambler is a device that encodes or randomizes messages at the transmitter to make it unintelligible at receivers that are not equipped with appropriate descrambling device. Scrambling is widely used in satellite, radio relay communications and PSTN modems. In the DVB system the complete BBFRAME is randomized. The randomization sequence is synchronous with the BBFRAME

starting from the MSB and ending with KBCH bit. Figure 3.5 the scrambling sequence is generated by the feed-back shift register. The polynomial for the Pseudo Random Binary Sequence (PRBS) generator is:

$$1 + X^{14} + X^{15}$$

Figure 3.6: PRBS Implementation [29]

### 3.2.2 Bit Interleaved Coding and Modulation (BICM)

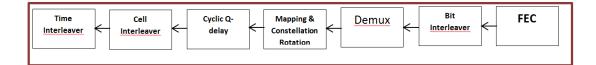

The Bit Interleaving Code Modulation is the second block of the DVB-T2 system. It consists of seven blocks as shown in figure 3.7.

Fig. 3.7: BICM Block Diagram

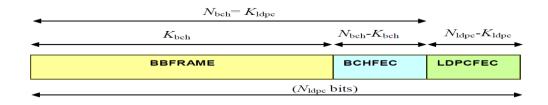

### 3.2.2.1 FEC encoding

This sub-system shall perform outer coding (BCH), Inner Coding (LDPC) and Bit interleaving. The input stream shall be composed of BBFRAMEs and the output stream of FECFRAMEs. Each BBFRAME ( $K_{bch}$  bits) is processed by the FEC coding subsystem, to generate a FECFRAME ( $N_{ldpc}$  bits). The parity check bits (BCHFEC) of the systematic BCH outer code is appended right after the BBFRAME, and the parity check bits (LDPCFEC) of the inner LDPC encoder shall be appended after the BCHFEC field, as figure 3.8 illustrates.

Fig. 3.8: format of data before bit interleaving [29]

### • Outer encoding (BCH)

The outer coding BCH (Nbch, Kbch) code is the first encoding stage. It is applied to each BBFRAME for an error protected packet generation.

In coding theory, the BCH codes form a class of cyclic error-correcting codes that are constructed using finite fields. BCH codes are invented in 1959 by French mathematician Alexis Hocquenghem, and independently in 1960 by Raj Bose and D. K. Ray-Chaudhuri. The acronym BCH comprises the initials of inventors' names [29].

One of the key features of BCH codes is that during code design, there is a precise control over the number of symbol errors correctable by the code. In particular, it is possible to design binary BCH codes that can correct multiple bit errors. Another advantage of BCH codes is the ease with which they are decoded, namely, via an algebraic method known as syndrome decoding. This simplifies the design of the decoder for these codes, using small low-power electronic hardware. BCH codes are used in applications such as satellite communications, compact disc players, DVDs, disk drives, solid-state drives and two-dimensional bar codes.

### • Inner Encoding (LDPC)

The LDPC concept is developed by Robert G. Gallager in 1960. (LDPC) code is a linear error correcting code. It is the second encoding stage. LDPC codes are capacity-approaching codes which means that practical constructions exist that allow the noise threshold to be set very close to the theoretical maximum. The noise threshold defines an upper bound for the channel noise, up to which the probability of lost information can be made as small as desired. Using iterative belief propagation techniques, LDPC codes can be decoded in time linear to their block length [2].

LDPC codes are finding increasing use in applications requiring reliable and highly efficient information transfer over bandwidth or return channel-constrained links in the presence of corrupting noise. Implementation of LDPC codes has lagged behind that of other codes, notably turbo codes.

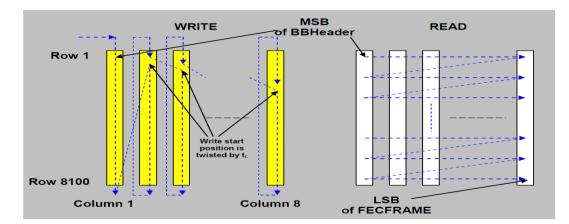

### **3.2.2.2 Bit Interleaver**

Interleaving is a technique for making forward error correction more robust with respect to burst errors. The output of the LDPC encoder is fed through a bit interleaver. The bit interleaver consists of parity interleaving followed by column twist interleaving. The bit interleaver is the second BICM stage.

In the parity interleaving part, parity bits are interleaved by [2]:  $u_i = f_i \text{ for } 0 \le i < k_{ldpc} \text{ (information bits are not interleaved)}$  $u_{kldpc} + 360t + s = f_{kldpc} + Q_{ldpc} * s + t, \text{ for } 0 \le s < 360, 0 \le t < Q_{ldpc}$

where u is the parity interleaving output and  $Q_{ldpc}$  is defined in table 3.1

| Code Rate | Q <sub>ldpc</sub> |

|-----------|-------------------|

| 1/2       | 90                |

| 3/5       | 72                |

| 2/3       | 60                |

| 3/4       | 45                |

| 4/5       | 36                |

| 5/6       | 30                |

Table 3.1: QLDPC values for normal frames

In the column twist interleaving part, the data bits ui from the parity interleaver are serially written into the column-twist interleaver column-wise, and serially read out row-wise (the MSB of BBHEADER is read out first) as shown in Figure 3.9, where the write start position of each column is twisted by  $t_c$  according to table 3.2. This interleaver is described by the following [2]:

The input bit  $u_i$  with index *i*, for  $0 \le i \le N_{\text{ldpc}}$ , is written to column  $c_i$ , row  $r_i$  of the interleaver, where:

$$c_i = i \operatorname{div} N_r$$

$$r_i = i + t_c \mod N_r$$

The output bit  $v_i$  with index j, for  $0 \le j < N_{ldpc}$ , is read from row  $r_j$ , column  $c_j$ , where

$r_{j} = j \operatorname{div} N_{c}$  $c_{j} = j \operatorname{mod} N_{c}$

Fig.3.9: Bit interleaving scheme [29] Table 3.2: Column twisting parameter *t*c [2]

| Modulation | Columns        | N <sub>ldpc</sub> |        | Twisting parameter <i>t</i> <sub>c</sub> |   |   |    |    |    |    |    |    |    |    |    |    |    |    |

|------------|----------------|-------------------|--------|------------------------------------------|---|---|----|----|----|----|----|----|----|----|----|----|----|----|

| Modulation | N <sub>c</sub> | 1 dpc             | Col. 0 | 1                                        | 2 | 3 | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

| 16-QAM 8   | 64 800         | 0                 | 0      | 2                                        | 4 | 4 | 5  | 7  | 7  | -  | -  | -  | -  | -  | -  | -  | -  |    |

|            | 16 200         | 0                 | 0      | 0                                        | 1 | 7 | 20 | 20 | 21 | -  | -  | -  | -  | -  | -  | -  | -  |    |

| 04.0414    | 12 64 80       | 64 800            | 0      | 0                                        | 2 | 2 | 3  | 4  | 4  | 5  | 5  | 7  | 8  | 9  | -  | -  | -  | -  |

| 64-QAM     | 12             | 16 200            | 0      | 0                                        | 0 | 2 | 2  | 2  | 3  | 3  | 3  | 6  | 7  | 7  | -  | -  | -  | -  |

| 256 OAM    | 16             | 64 800            | 0      | 2                                        | 2 | 2 | 2  | 3  | 7  | 15 | 16 | 20 | 22 | 22 | 27 | 27 | 28 | 32 |

| 256-QAM    | 8              | 16 200            | 0      | 0                                        | 0 | 1 | 7  | 20 | 20 | 21 | -  | -  | -  | -  | -  | -  | -  | -  |

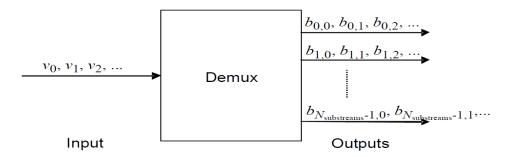

### 3.2.2.3 Bit to cell word de-multiplexer

The input bit-stream from the bit interleaver is de-multiplexed into N-substreams, as in figure 3.10. The number of N-substreams depends on the modulation employed as in table 3.3.

| Modulation | N <sub>Idpc</sub> | Number of sub-streams,<br>N <sub>substreams</sub> |

|------------|-------------------|---------------------------------------------------|

| QPSK       | Any               | 2                                                 |

| 16-QAM     | Any               | 8                                                 |

| 64-QAM     | Any               | 12                                                |

| 256-QAM    | 64 800            | 16                                                |

| 256-QAM    | 16 200            | 8                                                 |

Fig. 3.10: De-multiplexing of bits into sub-streams [29]

# **3.2.2.4 Mapping and Constellation Rotation**

The demux output for Each FECFRAME (which is a sequence of 64 800 bits for normal FECFRAME, or 16 200 bits for short FECFRAME) is then mapped into a constellation diagram as shown in figure 3.11. The input bits are grouped into cell of  $\eta$ mod bits. Every modulation has a certain number of bits per cell as table 3.4 shows.

| LDPC block length<br>(N <sub>Idpc</sub> ) | Modulation mode | η <sub>MOD</sub> | Number of output<br>data cells |  |  |

|-------------------------------------------|-----------------|------------------|--------------------------------|--|--|

|                                           | 256-QAM         | 8                | 8 100                          |  |  |

| 64 800                                    | 64-QAM          | 6                | 10 800                         |  |  |

| 64 800                                    | 16-QAM          | 4                | 16 200                         |  |  |

|                                           | QPSK            | 2                | 32 400                         |  |  |

|                                           | 256-QAM         | 8                | 2 025                          |  |  |

| 16 200                                    | 64-QAM          | 6                | 2 700                          |  |  |

| 10 200                                    | 16-QAM          | 4                | 4 050                          |  |  |

|                                           | QPSK            | 2                | 8 100                          |  |  |

Table 3.4: Parameters for bit-mapping into constellation [29]

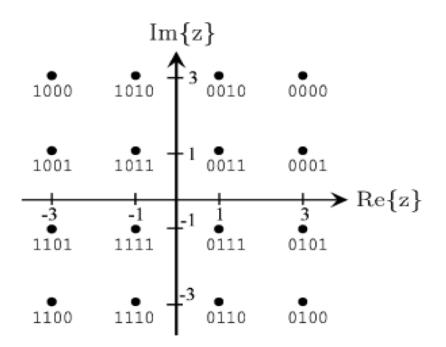

Figure 3.11: 16 QAM constellations [29]

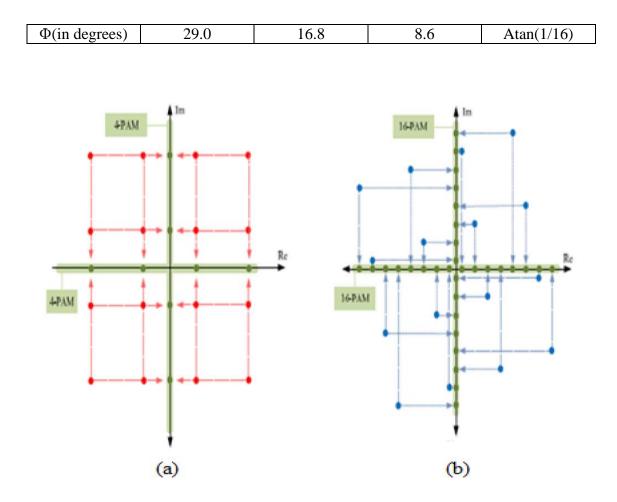

When a constellation signal is transmitted in fading conditions, both real (I) and imaginary (Q) face the same fading. Thus, in case of severe fading, the information transmitted on I and Q channels suffer from an irreversible loss. In case of the rotated constellation, a certain rotation angle is applied in the complex plane to a classical signal constellation to uncorrelate between the two components.

The rotating of the constellation is done by the output cells G, where  $G = (g_0, g_1, ..., g_{Ncells-1})$  are given by [1]:

$$g_0 = Re(R_{RQD}f_0) + jIm(R_{RQD}f_{N_{cells}-1})$$

$$g_q = Re(R_{RQD}f_q) + jIm(R_{RQD}f_{q-1})$$

where  $f_0$  and  $f_q$  are the first and last cells respectively within the constellation diagram, RRQD is the phasor rotation angle and  $\Phi$  is the rotation angle. Values of different  $\Phi$  for different modulation techniques are in table 3.5. Figure 3.12 illustrates the classical constellation diagram and a rotated constellation diagram.

Table 3.5: Rotation angle for each modulation Type

| Modulation | QPSK | 16-QAM | 64-QAM | 256-QAM |

|------------|------|--------|--------|---------|

|            |      |        |        |         |

Figure 3.12: a) Classic 16-QAM constellations with projections in axis (2x 4-PAM). b) Rotated 16-QAM constellations with projections in axis (2x16-PAM) [29].

### 3.2.2.5 Cyclic Q-Delay

Cyclic Q delay is one of the optional modules that is used in DVB-T2. The cyclic q delay input is a stream of cells that represents the constellation rotation output. The main role of the cyclic Q delay module is to uncorrelate the real and imaginary parts (in-phase (I), quadrature (Q)) components of every constellation point especially in severe fading environment. The cyclic Q- Delay works on the

constellation rotated data  $C_{in} = (C_{in1}, C_{in2}, ..., C_{in Ncells})$  and it delays the imaginary part by one cell. The output of the cyclic Q delay is referred to as  $Co = (C_{o1}, C_{o2}, ..., C_{o Ncells})$ , where  $C_o$  is given by:

$$Co = Re (C_{in i}) + j Im(C_{in i+1})$$

where i takes on the values 1, 2, 3  $\dots$  N<sub>cells</sub>. Fig.3.13 gives an illustration for the operation taking place in cyclic Q delay.

Fig.3.13: Cyclic Q-delay process [28]

### **3.2.2.6 Cell Interleaver**

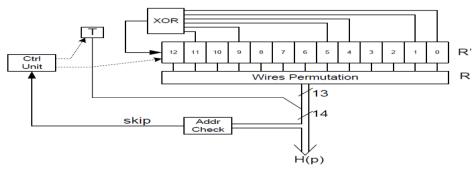

The main goal of the interleaving process is to spread the content in the time/frequency plane, such that neither impulsive noise nor frequency-selective fading would cause a long sequence of the original data stream to be erased. The cell interleaving process applies a pseudo-random permutation in order to uniformly spread the cells in the FEC code word.

The input cells to the cell interleaver take a new index generated from the pseudo random process. The Pseudo Random Cell Interleaving process that is done by the cell permutation is used to ensure an uncorrelated distribution of channel distortions in the receiver.

The input to the cell interleaver is the data cells  $C_o = (C_o \ i, \ C_o \ 2,..., \ C_o \ Neells)$  is generated by the constellation rotation and cyclic Q delay process. The output of the cell interleaver is a vector referred to as  $CI_o(j) = (CI_o \ j, l, \ CI_o \ j, 2, \ CI_o \ j, 3,..., \ CI_o \ j, Neells)$ . The vector is defined by:  $CI_o \ j, Sj(i) = C_o \ j, i$ , where  $i = 1, 2, ..., N_{cells}$  and  $S_j(i)$  is the permutation function applied to FEC block j of the Time interleaver block  $S_j(i) = [S_1(i) + P(j)] \mod N_{cells}$ , where  $S_1(i)$  is the basic permutation function and P(j)is the shift value to be used in FEC block j. For example for  $N_{cells}$ = 10800, 64 QAM, the shift P(j) is to be added to the permutation for j =1, 2, 3, etc. is 1, 8 193, 4 097, 2 049, 10 241, 6 145, 1 025, 9 217, etc. Figure 3.14 illustrates the cell interleaving process.

Fig. 3.14: Cell Interleaver process [29]

### 3.2.2.7 Time Interleaver

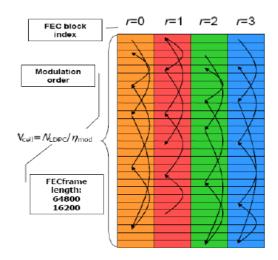

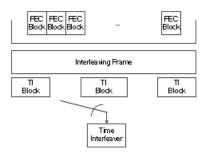

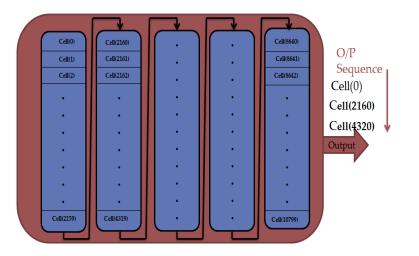

The cell interleaved data is introduced as an input to the time interleaver. The time interleaving process is similar to the bit interleaving process. In DVB-T2, the Forward Error Correction (FEC) blocks, for each PLP, are grouped into interleaving frames for time interleaving purposes. Each TI block contains a dynamically variable integer number of FEC blocks that are interleaved before transmission. The Time Interleaver (TI) operates at the PLP level. The parameters of the time interleaving Frame is either mapped directly onto one T2-frame or spread out over several T2-frames. There are three options for time interleaving for each PLP. First, each Interleaving Frame contains one TI-block and is mapped directly to one T2-frame as in Single PLP case. This gives maximum data rate. Third, each Interleaving Frame contains one TI-block and is mapped to more than one T2-frame as shown in figure 3.15.

Figure 3.15: Time Interleaving Implemented in DVB-T2 [29]

The Time Interleaver is a row-column block interleaver. The number of bits of LDPC coded block Nldpc is 64 800 bits for normal FECFRAME, or 16 200 bits for short FECFRAME. The number of rows Nr in the interleaver is equal to the number of cells in the FEC block (Ncells) divided by 5 as table 3.6 shows [29].

| LDPC block length<br>(N <sub>ldpc</sub> ) | Modulation<br>mode | Number of cells<br>per LDPC block<br>(N <sub>CELLS</sub> ) | Number of rows <i>N</i> <sub>r</sub> |

|-------------------------------------------|--------------------|------------------------------------------------------------|--------------------------------------|

|                                           | 256-QAM            | 8 100                                                      | 1 620                                |

| 64 800                                    | 64-QAM             | 10 800                                                     | 2 160                                |

| 04 000                                    | 16-QAM             | 16 200                                                     | 3 240                                |

|                                           | QPSK               | 32 400                                                     | 6 480                                |

|                                           | 256-QAM            | 2 025                                                      | 405                                  |

| 16 200                                    | 64-QAM             | 2 700                                                      | 540                                  |

| 16 200                                    | 16-QAM             | 4 050                                                      | 810                                  |

|                                           | QPSK               | 8 100                                                      | 1 620                                |

Table 3.6: The number of rows for different modulations [29]

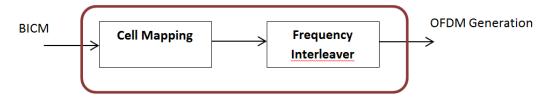

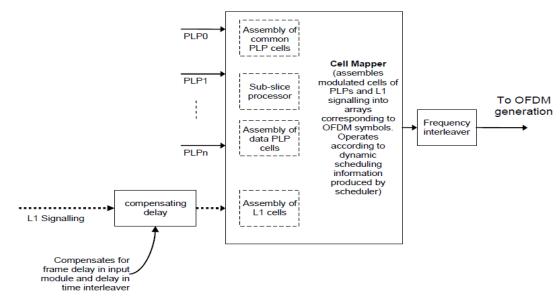

# 3.2.3 Frame Builder

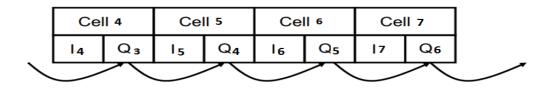

The frame builder block consists of 2 stages. It starts by cell mapping followed by frequency interleaving stage as shown in figure 3.16. The cell mapper maps cells